关于28950波形的疑问

本人采用28950进行电源设计,按照网上的推荐设计,

现在发现3个问题,第一是我无论改变SS引脚的C015电容的大小,最大增大到过100U,都无法实现占空比缓慢启动的过程,第二,我改变RSUM引脚的电阻,15K和13K两个电阻,对于我最大占空比产生很大的印象,图一为15K最大占空比,图2为13K最大占空比。

第三个问题,在带载过程中,发现在带到一定负载的时候,输出电压自己升高了,占空比增大了,但是占空比是稳定的。希望大家帮忙分析下为什么!非常感谢

第一是我无论改变SS引脚的C015电容的大小,最大增大到过100U,都无法实现占空比缓慢启动的过程,

A: 请提供启动时,PWM与SS电压的波形。去掉R205试试。

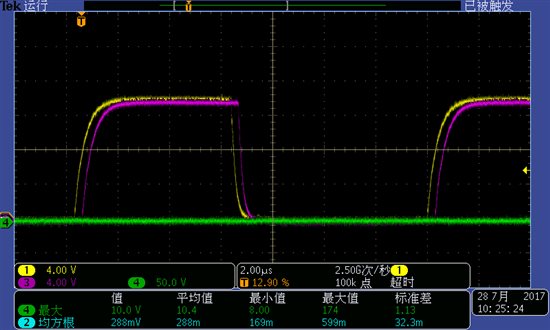

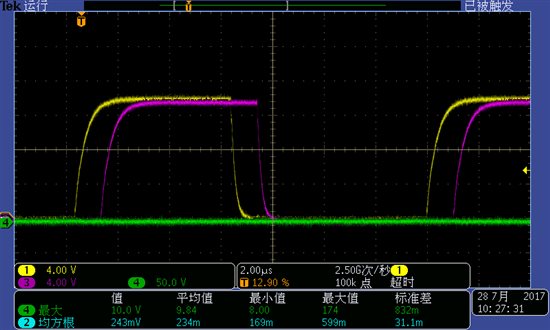

第二,我改变RSUM引脚的电阻,15K和13K两个电阻,对于我最大占空比产生很大的印象,图一为15K最大占空比,图2为13K最大占空比。

A: 不建议将RSUM放的太小,斜波注入量增加,会影响最大占空比。Datasheet Fig 37可以看出,10k~20k的RSUM,注入量的变化会比较大。

第三个问题,在带载过程中,发现在带到一定负载的时候,输出电压自己升高了,占空比增大了,但是占空比是稳定的。希望大家帮忙分析下为什么

A:请提供更加具体点的测试条件,1,从多少负载变化到多少负载?2,电压升高了多少?3. EA+的电压在这个情况下的电压分别是多少?

1.去掉过R205,效果也一样,曾经观察过SS的波形,是由缓慢启动的,但是时间很短,占空比从0到最大只有延时30ms左右,然后改变电容大小对这个30ms没有影响

2.因为调试原因,大的电阻对于产品带载的稳定性有影响,而小电阻在产品带载过程中式可以稳定驱动的

3.通过观察第1引脚VREF的电压,我发现在产品没有电压升高的时候是5V,但是在出现问题的时候,电压升到6V以上,请问芯片的基准电压为什么会升高?

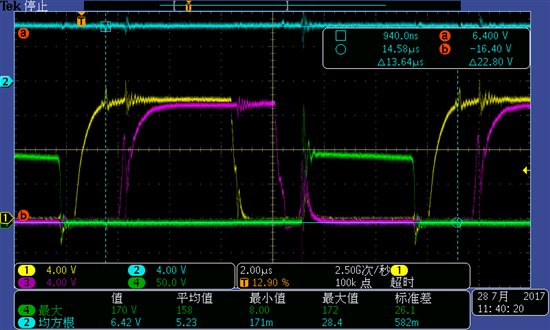

蓝色为产品1脚的基准电压5V,在出现问题的时候电压升高到6V以上

进一步观察,我改变了芯片2引脚的电压,由另外单独的12V供电输入,经过分压后得到2.5V后提供给引脚2,产品在带载到1400瓦时候,基准电压还是5V,当增加到1450瓦时候,基准电压(1引脚的5V)开始缓慢升高,当1引脚电压升高到6V时,产品开始驱动不稳定。为什么产品的基准电压会随着我增加负载而变化呢

去掉那两个二极管。

1. 去掉Q17,抓一下不同SS电容时的SS,PWM的波形。

2. 大电流不稳定,你需要去查电流环相关的问题。是不是PCB Layout或参数不当,导致大电流的情况下不稳定。你增加斜波注入不是合适的方法。

Q17和不用的二极管都已经去掉了,

可是为什么在不同电流下回导致芯片1引脚的VREF产生变化呢?1引脚不应该在任何条件下都保持在5V吗?我实际测量过,我输出在1410瓦的时候还正常,到1420瓦的时候1引脚就开始升高,只有10W的负载变化。可是基准电压不应该变化吧

有可能是功率加大之后,芯片受到干扰了。

1. 你需要看一下你芯片的PCB Layout, 有没有按我们的Datasheet中的PCB Layout进行布局。附近是否有较强的干扰源。

2. 可以加大REF的电容看看,是否有改善。

Hi

确实可能是layout问题。

我最大把VREF的电容增加到10U,没有效果,因为电压是整体上移的,并不是因为带载多导致的毛刺多,所以感觉增加电容并没有效果,

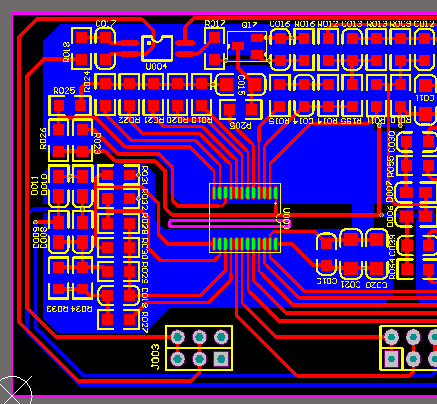

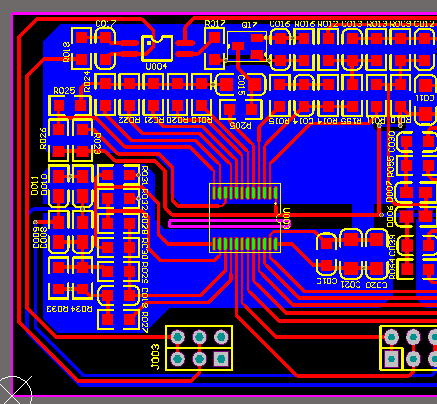

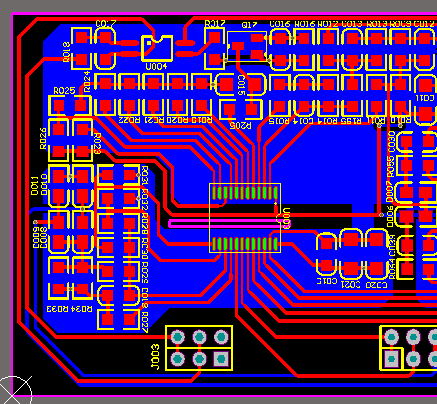

控制板和主功率板式分开的2个线路板,这个是控制板的布局

这个是控制板的布局图,控制板和功率板是分开的2个线路板

加大过VREF的电容,最大试过10UF,没什么什么效果,因为电压是整体提升,并不是毛刺,所以电容的作用感觉很小,对于布局,我的控制板布局图

控制板和功率板是2个独立的线路板,靠接插件焊接到一起

你说的改变SS端电容无法改变占空比缓慢启动,指的是OUTA、OUTB、OUTC、OUTD四个管脚的驱动波形无法缓慢启动还是指他们的移相角度无法缓慢启动?

相移角度无法缓慢启动,启动后,A和C很快就达到最大重叠

增大SS端电容,SS端上升波形没有变化?

增大SS端电容,SS的上升波形是由变化的,但是移相角还是没什么变化,我SS端电容增大到20UF,可是A和D两个驱动大约10ms就达到重合了。

电容改变前后,请提供SS波形及驱动的波形,在同一时间轴,抓全局及细节波形(启动开始,中间,后段)。