LM43603输出错误

在使用LM43603芯片时,设计要求是VIN=24V,VOUT=5V,IOUT=0.5A。但在实际使用时,负载加100K欧姆的电阻,测量的输出电压只有1.16V,其中VFB只有0.248V。测量的VCC=3.33V。请问一下,是由于什么原因导致的?怀疑是反馈的问题,但Rfbt=1M,Rfbb=255k,反馈电阻没有问题啊。

顺便问一下,LM43603在轻负载时的功耗大概有多大?

LM43603的电路图如附件所示。

谢谢!

你好,

反馈电阻可以改小十倍,另检查下是不是焊接的问题。

Hi

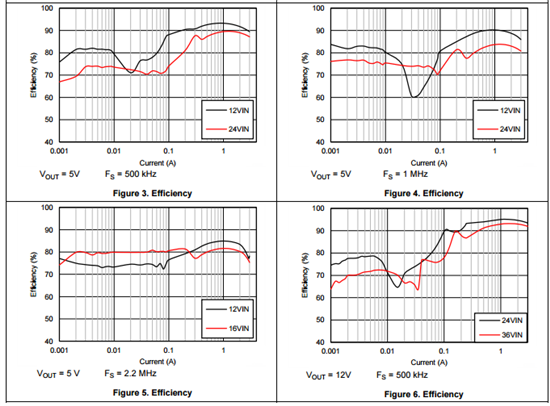

轻载功耗可以参考轻载效率大致估算:

完全无法带载,可能与你layout有关,将layout传上来看一下? 顺便将输出波形或者SW波形传上来看一下?

Hi

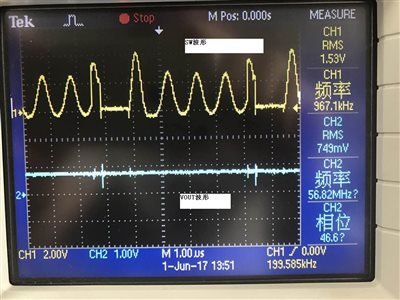

将反馈电阻改小(Rfbb=30k,Rfbt=120k;Rfbb=3k,Rfbt=12k)以后的VOUT均为0.75V,Vfb=0.149V。当Rfbb=3k,Rfbt=12k时,输出波形和电感前级的SW波形如下图所示。

我将反馈电阻Rfbb和Rfbt颠倒了一下,测得的VOUT=0.75V,Vfb=0.600V。

将反馈电阻全部去除,测得的VOUT=0.75V,Vfb=1.354V。

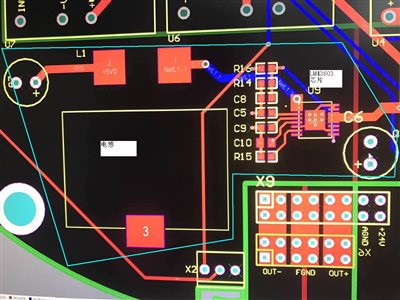

layout如下图蓝色框线内。

在焊接时,Cboot即CC5为680nf,CFF即C8未焊接。

这SW波形明显乱了。且逻辑是错的,你SS加个电容到地,看看SS波形。

Hi

将11脚SS与地之间加100nF,11nF,2.7nF,22pF,VOUT输出=0.75v,还是没有变化。

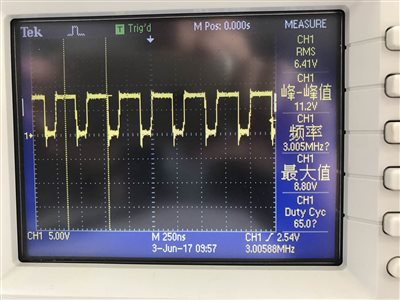

然后我将5脚bias断开,连接外部5V电源,输出正常的5.08V,此时Vbf=1.01V。11脚SS与地之间加22pF电容,Rt=205kHz。测量的SW波形如下图。但为什么SW频率、高电平、占空比和预设的(200kHz、24V输入、20.8%)不一致?

如果我只用一个外部电源24V(不使用5V外部电源)时,该怎么让LM43603正常输出?

你好,将BIAS连接到输出电容之后

你这个电路有个最基本的问题:输入输出电容。

输入端电容需要有陶瓷电容去耦,确保内部电路正常工作,建议加一个1uF的陶瓷在VIN和GND脚位附近。

输出电容目前只有一个电解,有电解的ESR很大,而这个电路并没有补偿极点,无法保证能够稳定工作。建议换成几十uF的陶瓷电容。

Hi

我已经在输入和输出端加上电解电容和0.1uF的陶瓷电容,结果只是输出纹波减小了,输出还是不正确。正在买47uF的陶瓷电容,等到了再试试。

对反馈部分的极点补偿,以增强环路稳定性,这部分有没有什么文档可以推荐的?

然后反馈部分是采用电压还是电流的方式?我在布板时,将电感和反馈电阻布得较近,会不会对输出有影响?

将BIAS连接到输出电容之后是什么意思?是BIAS与输出VOUT相连吗?

芯片是内部补偿的,增加极点比较复杂,不建议去加。内部补偿是按照低ESR的输出电容来设计的,故输出改成陶瓷等低ESR电容就行了

你好,这是峰值电流检测模式,内部有电流环和电压环共同反馈。电流模式下,ESR对重载的环路影响较大

对于FB和BIAS 管脚,一定要连接到输出电容之后,因为如果电感与输出电容的连线较长,那么在电感之后的波形没有输出电容之后的波形干净,信号进入芯片容易造成误动作。

还有,我在你的layout中没有找到FB和BIAS管脚连接Vout的铜线,是根据你的原理图建议你将他们连到输出电容之后。

对于输出电容,你可以参考datasheet的8.2.2.6. 输出电容的ESR也主要影响输出电压的overshoot和undershoot。

布的是四层PCB,将FB和BIAS管脚打过孔连接到中间层VOUT网络的。

RFBT与VOUT之间距离很近,RFBB与FB脚之间距离较远,这样的话,是不是反馈回路容易受电感影响?

对于输出电容的计算,参考的是datasheet的9.2.2.5?

感觉现在问题应该是定位在了反馈:输出电容的ESR要选择陶瓷电容和反馈回路的电阻布局。

不知道这样理解对不

你好, 是9.2.2.5

反馈电阻需要靠近FB管脚,参考章节11.2 中的版图设计,其中虚线是Vout到Rfbt的导线,这条线要接到输出Cout之后, 当然你的Vbais也需要接到Cout之后

同时信号环路(如反馈)需要靠近AGND管脚

同时电感一定要采用铁氧体功率电感