LM5119问题求助

如附件图所示,用LM5119做了一个30V转12V@30A的电源,发现在生产过程中不良率很高,维修发现主要是损坏LM5119的第2和第23脚,在板测量对地阻抗为100多欧,请教是什么原因造成这种不良,有什么办法避免?

TI的工程师呢,帮我分析分析吧,先谢谢了

Hi

低边驱动脚低阻抗了? 请问对应的低边MOS是否也烧掉了? Q5/6/7/8是否有损坏?

能否测试一下正常品Ho1和Lo1的波形,两通道同时测试,将波形传上来看一下。

我晚上回去测试上图。这一般是什么原因导致烧坏低边引脚?我原理图上的参数是否合理?有什么办法可以避免这样的问题发生,毕竟这芯片挺贵的,怎么感觉没有一点保护功能呢? 谢谢!

Hi

感觉上你的三极管设计上可能有些问题,其实你无需额外增加三极管加快放点,driver输出为低时放电效果不一定比三极管差。

具体你需要测试波形来确认。 另外请问你目前不良率是多少?

一般MOS驱动很难烧掉的,除非MOS烧掉。但在你的电路中MOS不一定烧掉了,或许只是三极管烧掉了。

是的,三极管烧掉了,MOS没有损坏 ,同时LM5119也烧掉了低边的脚(低阻抗了)。这里没有大电流,什么原因烧掉主芯片,损坏三极管 ?有没办法加入什么电路对芯片进行保护 ?

不良率我现在统计不了,有的板到客户手上,在使用过程中也会出现同样的不良。

Hi

损坏只在低边MOS驱动代表很可能是这边驱动设计的问题。

当低边驱动为低的时,MOS管子g极维持7.5V左右的电压(即三极管发射极电压), 而此时b极电压为0V, 7.5V的压差远远超过0.6V的管压降,这很可能导致三极管烧掉。

驱动是否烧掉,你要将三极管拿掉,或者单独测试芯片(拆下来的芯片)。

同时驱动2个MOS,你或需要选择Qg尽量小的MOS。

Johnsin,

这个线路图是TI原厂的代理商提供的,是原厂内部线路,不知道现在是否有升级的版本了,麻烦告知哪里有问题,需要做什么修正 ?

按您的说法,是否可以去掉这四个三极管,同时把四个二极管直接短路。

另外,在MOS管的GS极,有没有必要并一个10K左右的电阻,以防G极开环损坏MOS ,还是说在5119内部的驱动就有这个电阻了 ?

第一次试产算是比较失败的,接下来会进行二次试产,但二次试产需要在修正这个问题后,所以,希望得到你们技术的支援。

非常感谢!

Hi

建议在第二版中将三极管的放电电路去掉,同时选择Qg尽量小的MOS。

工作中驱动是否有震荡?驱动可以适当串联一个小的驱动电阻看看。

好的。期待……。

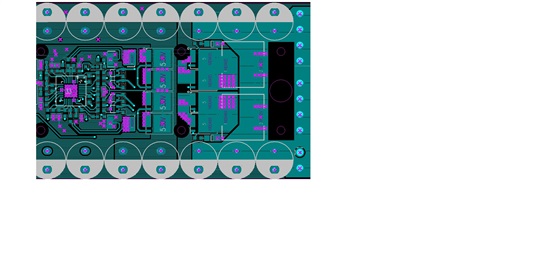

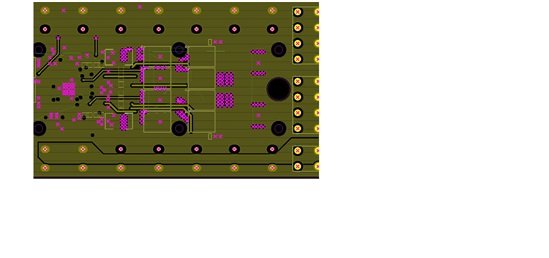

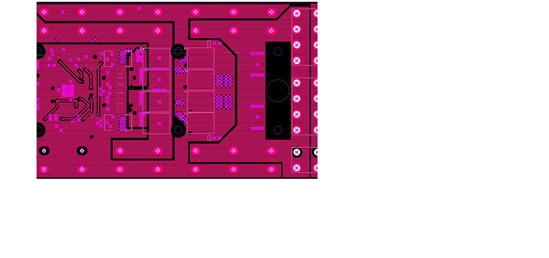

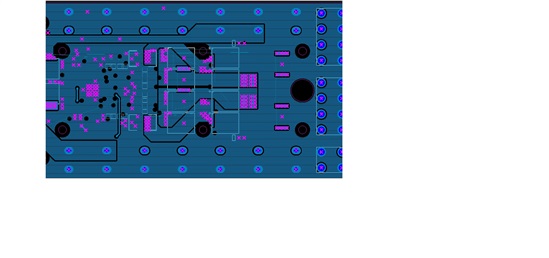

感觉这个板很不稳定,走的是四层板,会不会是layout有问题导致?实际布板有时无法按规格书中所述对地进行严格的划分,请帮我分析下这个板layout是否有问题。谢谢!PCB走线如下图;

有串过

我现在也在用5119做大功率降压电源,请问你遇到的问题解决了吗?

你试过去掉低边MOS驱动电路的二极管和三极管的运行效果吗?仿真软件设计的原理图没有这个结构。

去掉了这部分电路,目前另外一个问题。我跑100K的频率,输出12V,输出电流到20A的时候,电感啸叫严重

Johnsin,

我去掉三极管后,做了5个样板,问题还是没有得到解决,低端驱动对地短路的问题仍有存在。而且另外还有一个问题,25和27,30和32脚在老化测试后也发现有短路导致没有输出的情况。

请给点建议,什么原因会引起低端驱动脚对地短路?什么原因引起25和27,30和32脚在老化后短路?

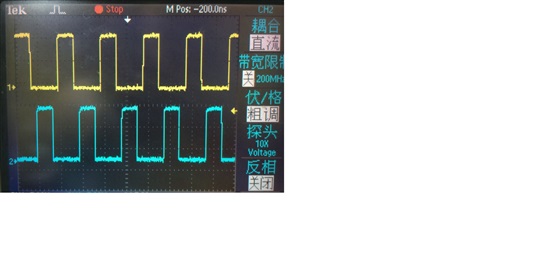

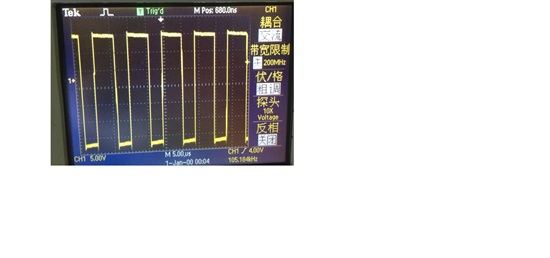

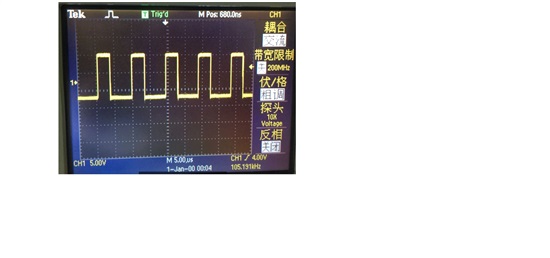

附件是正常的两个板测试的波形。(第一个图是空载的,下面两个图是30A负载的)

去掉三极管部分,故障依旧,那说明与三极管部分无关了。会不会与PCB布局和器件参数有关呢?我现在也在画这个芯片的PCB,我是按照TI的评估板的布局来设计的,器件也准备先按TI推荐的器件做实验,看看会不会出现你遇到的问题以及能不能达到评估板的效果。

第一幅图和后两幅图的耦合方式咋还不一样,后面两幅图咋用交流耦合?

加我QQ971217541。