UCD3138 用于 LLC 实验

时间:10-02

整理:3721RD

点击:

最近我使用UCD3138提供的范例Lab_4

成功把BUCK CLOSE LOOP

想尝试用在LLC电路

把Lab_4程式都改成Resonant

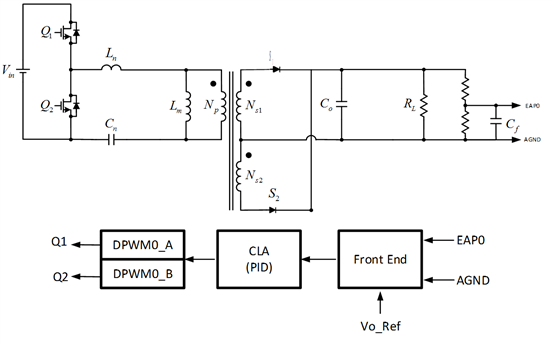

以下是我LLC电路:

但是我的DPWM0_A跟DPWM0_B没任何输出

请问是我程式的问题吗? 谢谢

main.c:

#define MAIN 1

#include "system_defines.h"

#include "Cyclone_Device.h"

#include "pmbus_commands.h"

#include "pmbus_common.h"

#include "pmbus_topology.h"

#include "variables.h"

#include "functions.h"

#include "software_interrupts.h"

#include "cyclone_defines.h"

#include "stdio.h"

void init_dpwm0(void)

{

Uint32 dead_time_1_local;

Uint32 dead_time_3_local;

Uint32 clamp_value;

dead_time_1_local = (pmbus_dcdc_config[0].dead_time_1 + 8) >> 4;

dead_time_3_local = (pmbus_dcdc_config[0].dead_time_3 + 8) >> 4;

clamp_value = (((Uint64)pmbus_dcdc_config[0].dead_time_2 * ((1 << 23) - 1)) / (pmbus_dcdc_config[0].max_period * 8));

Dpwm0Regs.DPWMCTRL0.bit.PWM_EN = 1; //1 = Enable PWM

Dpwm0Regs.DPWMCTRL0.bit.CLA_EN = 1; //1 = Enable CLA(PID)

Dpwm0Regs.DPWMCTRL0.bit.PWM_MODE = 1; //1 = Resonant Mode

Dpwm0Regs.DPWMCTRL0.bit.RESON_MODE_FIXED_DUTY_EN = 0; //0 = Duty cycle set by Filter duty

Dpwm0Regs.DPWMCTRL0.bit.CBC_ADV_CNT_EN = 0; //0 = PWM_A and PWM_B operate independently

Dpwm0Regs.DPWMCTRL1.bit.HIRES_DIS = 0; //0 = Enable High Resolution logic

Dpwm0Regs.DPWMCTRL1.bit.CHECK_OVERRIDE = 1; //1 = Disable //Bug

Dpwm0Regs.DPWMCTRL1.bit.EVENT_UP_SEL = 1; //1 = Update End Period Mode at End of Period

Dpwm0Regs.DPWMCTRL2.bit.RESON_DEADTIME_COMP_EN = 1; //1 = CLA Duty form Filter minus deadtime adjustment

Dpwm0Regs.DPWMCTRL2.bit.FILTER_DUTY_SEL = 2; //2 = DPWM Resonant Duty Register

Dpwm0Regs.DPWMPHASETRIG.bit.PHASE_TRIGGER = 2; //8ns phase delay

Dpwm0Regs.DPWMINT.bit.PRD_INT_SCALE = 2; //interrupt

Dpwm0Regs.DPWMINT.bit.PRD_INT_EN = 1; //interrupt

Dpwm0Regs.DPWMCTRL1.bit.GLOBAL_PERIOD_EN = 1; //1 = Event calculations use Global Period register

Dpwm0Regs.DPWMCTRL0.bit.MSYNC_SLAVE_EN = 0; //0 = PWM not synchronized to another PWM channel

LoopMuxRegs.DPWMMUX.bit.DPWM0_SYNC_SEL = 0; //0 = DPWM0 with DPWM0 Sync

Dpwm0Regs.DPWMPHASETRIG.all = 32; //128ns phase delay

Dpwm0Regs.DPWMEV1.bit.EVENT1 = dead_time_1_local;

Dpwm0Regs.DPWMEV2.bit.EVENT2 = pmbus_dcdc_config[0].min_period * 8 + dead_time_1_local * 16 - pmbus_dcdc_config[0].dead_time_2;

Dpwm0Regs.DPWMEV3.bit.EVENT3 = pmbus_dcdc_config[0].min_period * 8 + dead_time_1_local * 16;

Dpwm0Regs.DPWMEV4.bit.EVENT4 = pmbus_dcdc_config[0].min_period * 16 - pmbus_dcdc_config[0].dead_time_2 + dead_time_1_local * 16;

Dpwm0Regs.DPWMPRD.bit.PRD = pmbus_dcdc_config[0].min_period;

Dpwm0Regs.DPWMCYCADJA.bit.CYCLE_ADJUST_A = (int16)(-DEADTIME2);

Dpwm0Regs.DPWMCYCADJB.bit.CYCLE_ADJUST_B = (int16)(-DEADTIME2);

Dpwm0Regs.DPWMRESDUTY.bit.RESONANT_DUTY = (pmbus_dcdc_config[0].max_period + 1) >> 1;

Filter0Regs.FILTERYNCLPLO.all = clamp_value;

Filter1Regs.FILTERYNCLPLO.all = clamp_value;

LoopMuxRegs.FILTERKCOMPA.bit.KCOMP0 = pmbus_dcdc_config[0].max_period;

}

void init_filter0(void)

{

Filter0Regs.FILTERCTRL.bit.PERIOD_MULT_SEL = 1; //1 = KComp received from Loop Mux module

Filter0Regs.FILTERCTRL.bit.OUTPUT_MULT_SEL = 3; //3 = Resonant Duty value received from DPWM Module

Filter0Regs.FILTERCTRL.bit.FILTER_EN = 1; //1 = Enables Filter operation

Filter0Regs.FILTERCTRL.bit.OUTPUT_SCALE = 0; //0 = No shift

Filter0Regs.FILTERCTRL.bit.USE_CPU_SAMPLE = 0; //0= Filter Mode, input data received from EADC

Filter0Regs.FILTERKPCOEF0.bit.KP_COEF_0 = 1;

Filter0Regs.FILTERKICOEF0.bit.KI_COEF_0 = 1;

Filter0Regs.FILTERKDCOEF0.bit.KD_COEF_0 = 0;

Filter0Regs.FILTERKDALPHA.bit.KD_ALPHA_0 = -1;

Filter0Regs.FILTERKICLPHI.bit.KI_CLAMP_HIGH = 0x7FFFFF;

Filter0Regs.FILTERKICLPLO.bit.KI_CLAMP_LOW = 0;

Filter0Regs.FILTEROCLPHI.bit.OUTPUT_CLAMP_HIGH = 0x7FFFFF;

Filter0Regs.FILTEROCLPLO.bit.OUTPUT_CLAMP_LOW = 0;

//LoopMuxRegs.FILTERKCOMPA.bit.KCOMP0 = (PERIOD/2) >> 4; //KCOMP is at 4 ns, period is at 250 ps

}

void init_loop_mux(void)

{

LoopMuxRegs.FILTERMUX.bit.FILTER0_PER_SEL = 0; //0 = Filter0 form DPWM0

LoopMuxRegs.FILTERMUX.bit.FILTER0_KCOMP_SEL = 0; //0 = Filter0 form KCOMP0

LoopMuxRegs.DPWMMUX.bit.DPWM0_FILTER_SEL = 0; //0 = DPWM0 duty cycle(resonant period) from Filter0

LoopMuxRegs.DPWMMUX.bit.DPWM1_FILTER_SEL = 0; //0 = DPWM1 duty cycle(resonant period) from Filter0

LoopMuxRegs.DPWMMUX.bit.DPWM1_SYNC_SEL = 0; //0 = DPWM1 master sync with DPWM0 sync

LoopMuxRegs.FILTERMUX.bit.FILTER0_FE_SEL = 0; //0 = Filter0 form Front End0

LoopMuxRegs.LLENTHRESH.bit.CYCLE_CNT_THRESH = 0; //

//LoopMuxRegs.SAMPTRIGCTRL.bit.FE0_TRIG_DPWM0_EN = 1; //use DPWM0 for filter0 sample trigger

}

void global_enable(void) //P.188

{

LoopMuxRegs.GLBEN.all = 0x101;

}

void init_front_end0(void)

{

FeCtrl0Regs.EADCDAC.bit.DAC_VALUE = 0; //1bit=1.5625mV //range 0V~1.6V //Ref=0.8V

FeCtrl0Regs.EADCCTRL.bit.AFE_GAIN = 3; //

FeCtrl0Regs.EADCCTRL.bit.SCFE_CLK_div_2 = 0; //0 = 16MHz sampling

FeCtrl0Regs.EADCCTRL.bit.EADC_MODE = 0; //0 = Standard mode, EADC samples based on sample triggers from DPWM module

FeCtrl0Regs.EADCCTRL.bit.AVG_MODE_SEL = 2; //2 = 8x Averaging mode

FeCtrl0Regs.EADCCTRL.bit.AVG_SPATIAL_EN = 1; //

}

void main()

{

volatile unsigned int dummy;

if(GioRegs.FAULTIN.bit.FLT3_IN == 0)// Re-Check pin assignment (ADC_EXT/SYNC may be?)

{

clear_integrity_word();

}

MiscAnalogRegs.CLKTRIM.bit.HFO_LN_FILTER_EN = 0;

init_pmbus(0x58);

init_dpwm0();

init_filter0();

init_loop_mux();

init_front_end0();

global_enable();

for(;;)

{

pmbus_handler();

}

}

//#pragma INTERRUPT(c_int00,RESET)

void c_int00(void)

{

main();

}

我使用UCD3138OL64EVM-031 Rev.A

现在,问题解决了吗,我发现,我的控制板也是没有PWM输出波形

您好,我正在使用UCD3138,我想问一下您可有开发板?有的话哪儿买的?还有您的例程代码从哪儿得到的?方便告知吗?我急需啊

Hi

可以发成为新帖吗?