TPS65131负电源轨带载能力低

您好,TI社区的技术大牛们

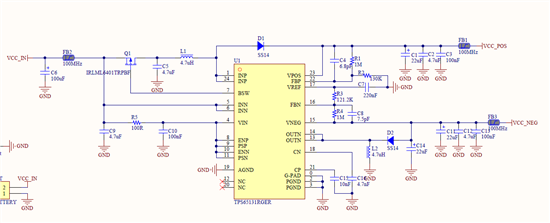

目前我使用TPS65131提供正负电源给后续电路供电时出现负电源带载能力不足的现象,VPOS=11.5,VNEG=-10.5,经单VNEG对GND使用负载仪测试发现,当负载电流增加到60mA时,电压在2秒内从-10.03V升到-3.29V,此时FBN引脚电压升到0.8V。OUTN引脚开关脉冲幅度大幅下降。此时VPOS电压不受影响,VPOS测试带载能力》500mA@100mV跌落。电路图如下。

目前怀疑是不是由于PSP/PSN上拉导致开启POWER_SAVE_MODEL下切换导致的问题?还是有其余设计上的问题,谢谢!

MOS管型号:IRIML6401; 二极管型号:SS14; 电感参数:4.7uH@100K,Isat=3.0A,Irms=2.2A

Hi

先测试一下正电压输出那组,用电子负载确认一下最高输出电流是多少? (如果5V输入可实现600mA左右输出。 你可以加载到300mA以上,目的是验证你的电感)

或者有条件测试一下电感的饱和电流,防止买到的电感有质量问题,这个很容易引起带载能力下降的问题。

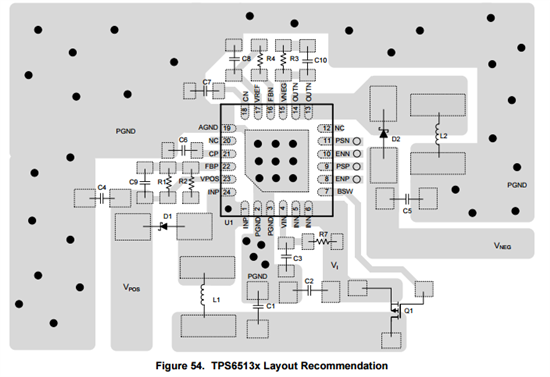

其次你或需要注意你的layout,例如功率路径尽量最小化, 输入电容尽量靠近芯片Vin脚,GNDlayout等。

Hi

先测试一下正电压输出那组,用电子负载确认一下最高输出电流是多少? (如果5V输入可实现600mA左右输出。 你可以加载到300mA以上,目的是验证你的电感)

或者有条件测试一下电感的饱和电流,防止买到的电感有质量问题,这个很容易引起带载能力下降的问题。

其次你或需要注意你的layout,例如功率路径尽量最小化, 输入电容尽量靠近芯片Vin脚,GNDlayout等。

您好, Johnsin

VPOS测试有写,4.2V输出11.5V@500mA电压跌落小于100mV,输出正常。

VPOS/VNEG用的电感式同样的型号,现在的问题就是负电源轨带载超过不了60mA.

Layout版图目前不在手上提供不了,不过设计阶段尽量按照较短路线考虑的。

芯片更换过,也是一样的结果。

补充下,二极管丝印画反了,实际焊接是按照电路图来的。

Hi

主要是电感(交换电感看看效果?)

其次电路图中电容极性反了,但是板子上应该不存在这个问题,否者空载不会正常。

您好,Johnsin

电感已更换,无效果。电容无误,丝印阴影处为正极性,因为是钽电容。

您好,Johnsin

近日继续调试发现TPS65131更加奇怪的问题,在VIN = 4.75V时,负电源带载能力只有60mA,而当电压降到3.3V时,带载能力能够达到200mA。

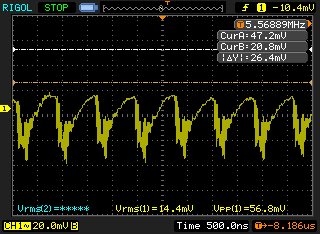

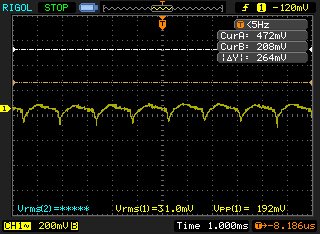

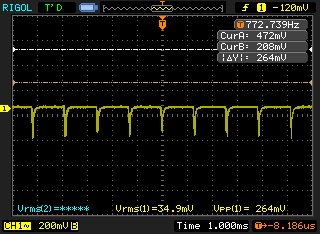

上图是输入电压3.3V@658mA,输出-10.1V@150mA处负载上的交流信号。

当维持负载电流不变,输入电压升高3.7V时,输出电流电压瞬降到0

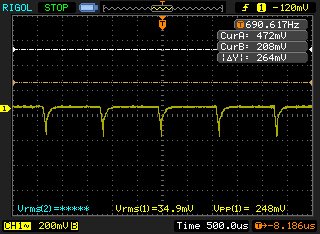

上图是输入电压3.69V@12mA,负载0V@150mA的波形。

稍微降低输入电压并重新对芯片上电,发现此时虽有一定带载能力但纹波很大。

上图为 输入3.59V@660mA,输出10.55V@150mA

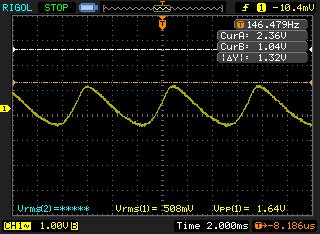

同理测试4.85V输入时带载波形,如下:

上图为 输入4.85V@139mA,输出9.31V@60mA

上图为 输入4.85V@7mA,输出0V@70mA

版图文件

目前无法确认问题原因,现象较怪。

Hi

从你的描述看,既不是芯片问题,也不是电路或者零件问题造成的,只能重新layout看看:( 感觉你的layout和datasheet上差别还是特别大的)

功率环路是会影响待在能力的。

好的,谢谢。我准备重新按照官方建议Layout试试