TPS51216输出问题

设计目标:

输入电压:5V

输出电压:1.8V

输出电流:4A 最大

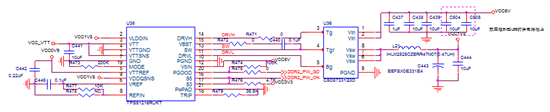

电路图如下:

问题现象:

首先将S3和S5置高,

测得电感后级输出稳定在0.736V,没有达到1.8V。使用万用表测量时,显示先到过1.8V后马上下降为0.736V

由于VLDOIN是接在1.8V上的,导致VTT和VTTREF都没有输出0.9V。

VREF输出电压为1.823V,VREFIN的电压也为1.823V。后将VREFIN的电压分压到1.5V,后级输出还是0.736V。

1.请问反馈电阻R477设置为10K,R478不焊接是否正确?

2.MOS管Vin接5V是否会影响输出?

3.电感取值是否合理?

对比了参考电路slur270.pdf中page7没有发现很大的区别,请指出设计中可能存在的问题,谢谢

1,关于反馈电阻和电感的取值建议参考数据手册SLUSAB9A, R478不能空着

2,MOS管接5Vin是可以

3, 建议抓取VSW节点的波形(分别在空载和重载条件下)

4, VTT和VTTREF这个内部的LDO没有输出是因为你的VCC1V8处电压不稳,所以你首先要解决的是开关电源的输出问题

1.因为TPS51216输出电压上限为1.8V,VREF输出的参考电压即为1.8V,

因此R477选取为10K后为了是REFIN为1.8V所以讲R478悬空,

如果R478必须要焊接电阻那么需要1M左右的电阻方能满足要求。

2.另外为了验证是否是R478导致输出不正确,在R478处焊接过50k左右的电阻,

将REFIN设置为1.5V,但是测量mos管后级的输出仍旧是0.736V,

所以怀疑是本身控制环路有问题,希望帮助复查在电阻、电容、mos管选型上是否需要优化。

另外boost管脚是否需要二极管进行上拉?

关于电感电容的取值参考数据手册上的公式即可。另外boot电容处可以不加上拉二极管,只要你V5IN进来的电压是稳定5V,其内部已经存在二极管了, 关于MOS选型只要保证其栅极驱动电压为为4V左右即可。

关于环路,由于该为DCAP控制,环路上只要注意输出电容的选取就可以。

建议在的VREFIN处再加一个小电容0.1uF左右

所以建议你可以将MOS管驱动电压波形, VREF和VEFIN处电压, VSW波形抓取一下, 谢谢

您好,

请问电感的耐流值选取的是多少?

电感选型为IHLM2525CZERR47M07(0.47UH) 饱和电流为25A

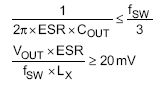

另外根据datasheet 第17页的稳态要求

目前mode管脚下拉电阻式200k,意味着switching frequency是400Khz

根据目前设计Cout为330uf左右,ESR估计为8毫欧

公式左侧1000000/(2*3.14*330*8)Khz=60

公式右侧400/3Khz=133

由于除了330uF以外还并联了其他小电容,等效电容值会更大,是可以满足稳态条件的。

另外是否根据上次的分析在R478处增加1M欧姆的电阻?

目前是根据根据datasheet手册21也的要求进行计算设计

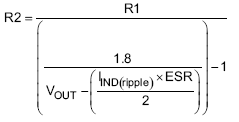

1.计算反馈电阻:

公式中R1取10K,就是原先原理图中的R477,由于输出Vout是1.8伏,公式中分子极小R2近似为无穷大

根据 Vental Mao的反馈R2不能浮空,所以选取了1兆欧的电阻尽心焊接;

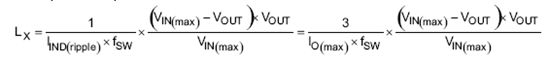

2.计算电感数值

(3/(12A*400K))*(5-1.8)*1.8/5=0.86uH,实际焊接值为0.47uh对应的Imax电流为18.38A左右

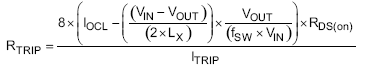

3.计算Rtrip,在室温环境下Itrip = 10uA,假设Iocl = 8A

MOS管的导通电阻为5.5毫欧

计算Rtrip = 8*(8-((5-1.8)/(2*0.47uH))*1.8/400/5))*5.5m/10uA = 21.71k 实际焊接36.5k,对应过载电流为11.36A

4.输出电容选择

实际选取松下poscap电容2R5THE330MF

电容值为330uf,耐压值为2.5V,ESR为15毫欧,后级芯片上的0.1uf和0.01uf小电容暂时不考虑在内

1/(2*3.14*330u*15m)=32.16k < 133.3k = 400k/3

1.8*15m/400k*0.47uh=143mV > 20mV

综上所示,在理论计算层面没有太大问题,但是后级mos端就是没有输出,请技术支持参考

各位TI工程师,能否根据目前我反馈的情况提供一个测试的思路

目前我觉得从设计角度排查没有找到不稳压问题的根本原因,请各位指点。

把DRVH和DRVL信号抓出来看看,看看驱动信号对吗?

请问有没有驱动节点波形的参考文档,我想参照后进行对比和分析,谢谢Max Han

因为这个芯片没有EVM,所以暂时没有

你可以测试后发出来,大家一起帮你看看

好的,谢谢Max Han。下周一会附上测试波形,届时希望各位工程师能够一起分析一下。

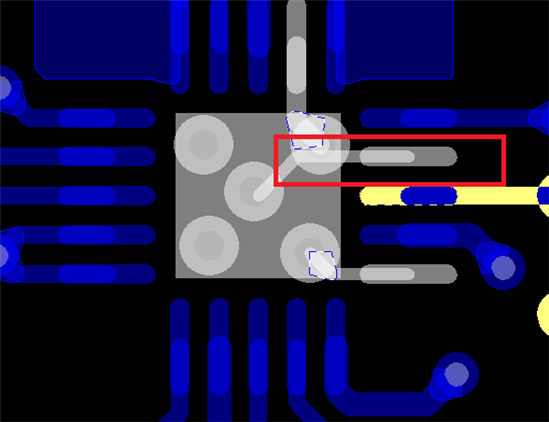

通过检查PCB布线发现TPS51216的pin7(GND)是直接连接到芯片底部的热焊盘上,

请问这样的连线是否会影响控制回路并引入噪声?

GND and PGND (power ground) should be connected together at a single point.

TPS51216哪些管脚一定要参考PGND呢?

如果没有单点接地是否会有非常大的影响,是否有补偿手段?

关于布局布线请参考数据手册的23-24页,里面有很详细的指导,谢谢

@Vental Mao

我是想问如果目前gnd和PGND没有实现单点接地的情况下是否会对后级的稳压产生决定性的影响?

你好,我没有遇见过您说的这种情况,但我从理论上理解是这样的:如果PGND和GND之间没有单点接地,而是通过长导线连接,这样就等效为PGND和GND之间存在电感,阻止了高频信号流向地。若高频信号的哦频率是落在该电路的穿越频率内,则会对电路的稳定性造成影响。 谢谢

@Vental Mao

目前GND和PGND是共地的,直接用过孔至地平面,而不是GND使用单点连接至PGND

所以附上的PGND和GND的PCB连接图,都是直接连接在一起打孔到地平面,如此做是否会影响环路的稳定性?

您所说的GND和PGND之间用长引线的情况目前不是的,而是出现多点接地的情况。

请答复

@Max Han @Vental Mao以及各位Ti工程师答复

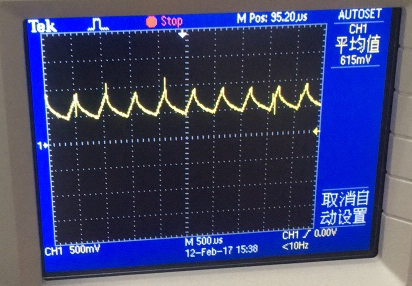

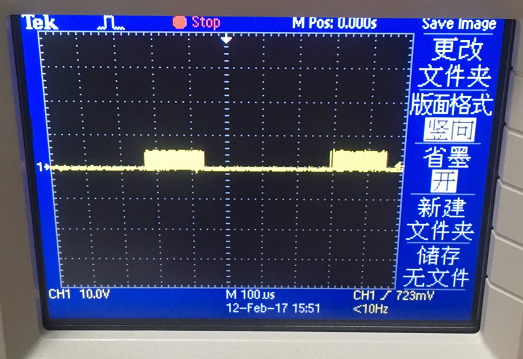

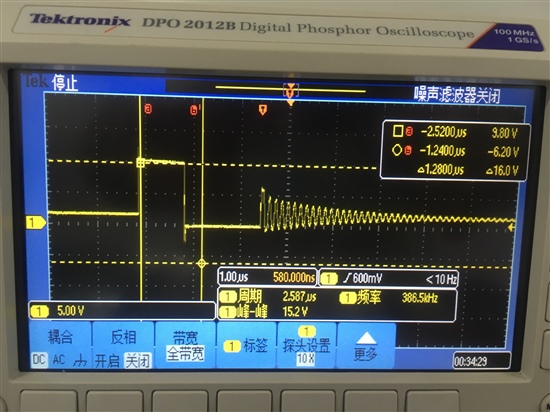

1.8V处波形,是否是电容失效了?测量点位sw后级,即电感和大电容交汇处,峰值都没到1V,有明显的三角波。

使用万用表测量时,均值电压0.736V,不管REFIN如何用电阻配置输出都是这个结果。

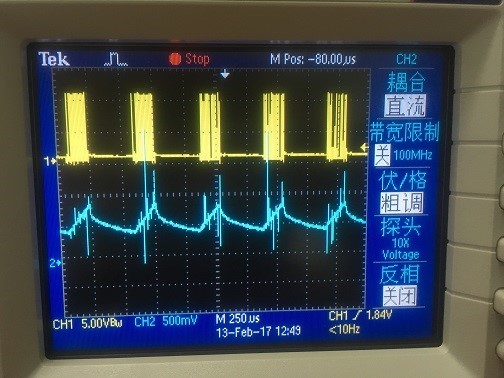

DRVH处波形,示波器10V每个,感觉开关频率是正确的,但是波形毛刺非常厉害

DRVL处波形,和上mos管栅极驱动波形一样,毛刺明显

是否意味着驱动线上的干扰非常严重?

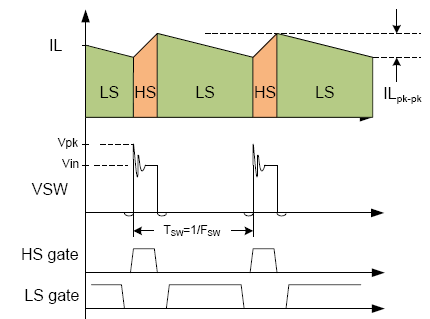

正常情况下的波形是应该如下的

目前上mos管和下mos管驱动线处有较大的干扰信号导致,输出电压不稳是否有改进措施?

请问如何能够判定干扰源在哪里?

另外根据Vental Mao所说

“如果PGND和GND之间没有单点接地,而是通过长导线连接,这样就等效为PGND和GND之间存在电感,阻止了高频信号流向地。”

我的理解是:需要在GND和PGND之间增加引线引入电感来屏蔽高频信号。

请问是否可以理解为干扰是由GND反馈至PGND么?(一般在PCB上面PGND才是和全局的“地”共在一起的)

要实现单线连接是否理解为芯片的pin7通过长引线连接至PGND(即整板的地)?

另外芯片底部的powerpad在连线时是作为GND对待还是PGND对待?

另外,我对图的注解有错误,mode管脚接的是200k

开关平率设置为400khz,周期应该为2.5us,从图中显示情况来看

应该认为tps51216的mos管驱动管脚不正确,时而有脉冲输出时而没有

而且信号有周期规律为500us,即2khz。

请问这个干扰源是从哪里来的?

这样接问题不大

你好,你的测试条件是什么,Vin, Vout, Iout。希望可以在示波器上同时显示DRVH和DRVL以及SW波形,谢谢

另外,最好也抓下输入电压波形, 从你之前给的图片来看,有可能是被保护,在一直重启,但是具体是什么保护看不出来,需要你更多的信息,谢谢

@Vental Mao

"这样接问题不大" 是指按照上次发的PCB中,PGND和GND直接共用电源层的解法问题不大么?

另外,想问一下datasheet上有一个light-load oepration的感念,如果负载脚清实际电流低于Iload(LL)是否会有图中现象?

(解决的方法是不是需要更换感值较大的电感)

@Vental Mao

目前测试条件是Vin为5V,Vout设计为1.8V,

假设每个内存颗粒最大电流是500mA,4颗工2A,CPU中的内存控制器需要380mA

总共设计最大为4.5A,综合波形之后会测量。

是的,可以这样接。

另外轻载模式下,该芯片波形也不会如你图片所示,该芯片轻载模式下SW波形和DCM模式下类似

另外,合理计算Rtrip电阻,确保OCL的电流值大于负载电流的波峰值。

同时在测试时,要保证稳压源的功率足以满足后续电路的功率消耗

@Vental Mao ,请参考

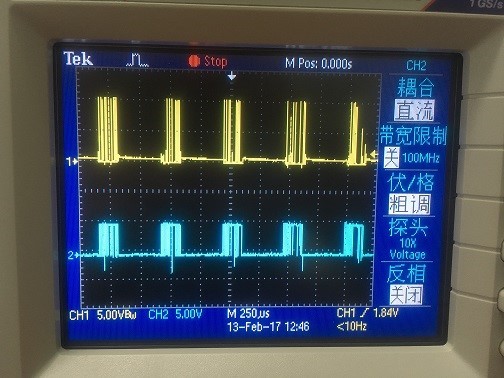

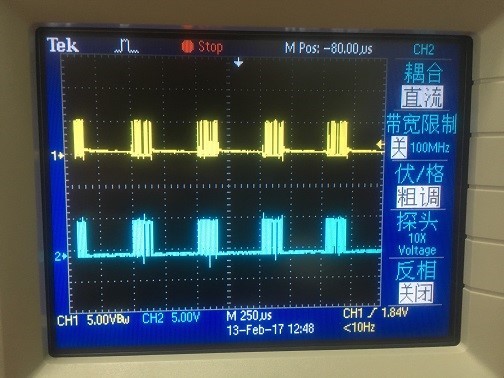

DRVH和DRVL处波形对比图

DRVL和SW对比图

DRVH和最终输出端对比图

你好,可以将时间轴的间隔变小么,最好可以同时显示SW ,DRVH, DRVL, 谢谢

另外方便测一下Vin的波形么

@Vental Mao

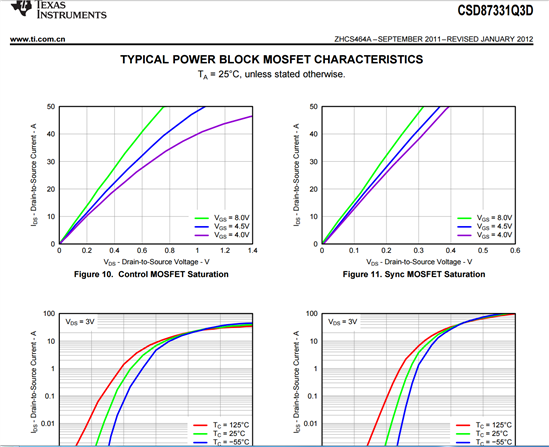

目前我想到一种可能是CSD87331Q3D的GS(th)为4.5V~8V,而我的Vin是5V可能无法保证栅极驱动的稳定

请问是否有封装兼容的GS(th) 1.4V~3V之间的MOS管?目前的封装是LSON-CLIP,请回复。

请问:

1.目前mos管的选型为CSD87331Q3D是否合适?(Vgs(th)为4.5伏)

2.在该mos管选型下,VIn设计为5V是否可以?(是否一定要大于8V,在8V~12V范围内取值)

从数据手册上来看,5V是没有问题的,还有决定MOS时候导通的电压是由V5in决定,而不是Vin(当然在你的图里面两个pin脚是连在一起的)

个人觉得应该还是你的输入端也就是Vin电压不稳,请测试Vin的电压波形

@Vental Mao

目前在mos管上加上12V电压,在输出端可以测得1.8V。

请问是否是由于占空比导致mos管工作有问题?

1.8/12和1.8/5,在mos管驱动是有何种却别?

两种情况下的占空比都属于正常工作范围之内,没有明显区别,

个人觉得是不是你把输入电压太高,你的稳压源输入功率也随之提高,就能带动后续负载。

你尝试在5V输入时,将稳压源的current limit设在3A,看是否得到正常的输出

@Vental Mao

目前在空载情况下测试,不论mos管接5V还是12V,终端都有输出,且为1.8V

带载之后不论12V还是5V给MOS管供电,输出端都没有输出。

经过测量,发现Drvl的信号质量较好,而drvh的信号干扰较大,请问是否有方法可以优化?

带载后无输出,是否是应为mos管本身的载流能力不足呢?

@Vental Mao

负载加重后,TPS51216的MOS管驱动波形的占空比会发生变化么?

在下mos管处是否需要增加续流二极管?

负载加重不会影响占空比的变化,

下mos管外加续流二极管可以让SW点的ring变小,对其带载能力影响不大(在mos导通的情况下)

带载后无法正常工作,一般有两种情况,一个是输入端功率不够,一个是芯片被保护了

对于DRVL信号较好,DRVH信号干扰较大,方便把波形上传一下么。主要原因估计还是因为其不是正常工作,所以驱动波形不正常。

空载时波形也是干扰较大么?

对于MOS管的带载能力,数据手册上显示的值带动你4A的负载是可以的

请问方便微信或者qq沟通么?时效性会强一些,交流也更加充分一些。

我的邮箱是lujunbiao@mcuris.com,如果可以请发联系方式给我,谢谢。

@Vental Mao

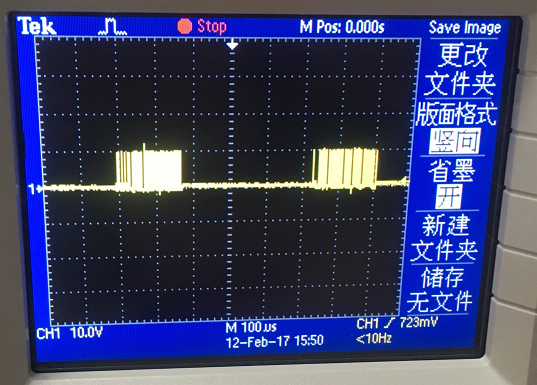

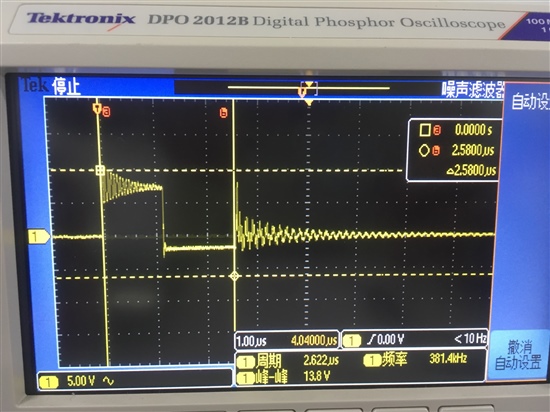

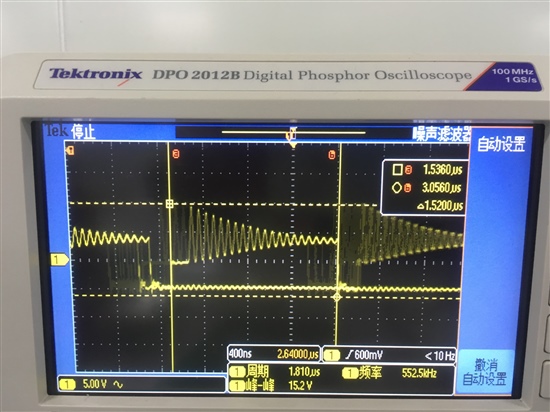

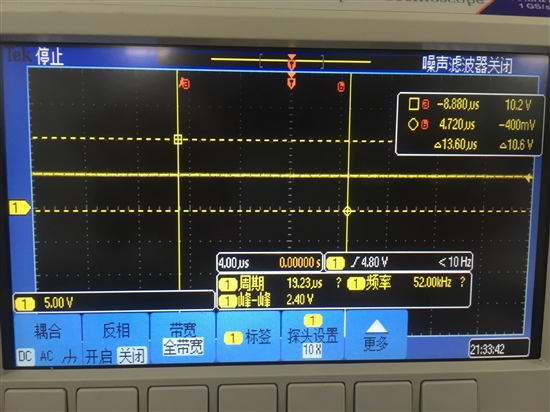

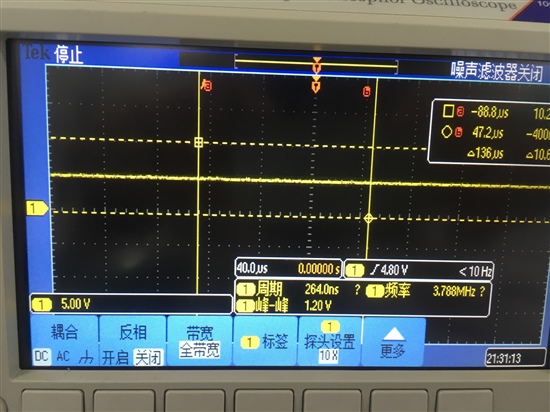

根据昨天情况,今天截取了2张轻载和重载下的DRVH的波形图,发现振铃现象明显

下图为轻载时候波形

下图为重载时候波形,由于输出没有到1.8V,可以看到DRVH上的干扰是很大的,请问是何种原因?

请问驱动端的高频信号是从哪里产生的?

高频信号的串扰路径流经哪些信号?

@Vental Mao

根据目前情况总结下来,DRVH信号在轻载的是否能够输出正确的占空比波形,由于轻载占空比波形不连续,后续的振铃波形不对后级稳压电路产生明显影响。

当负载增大到一定程度后,DRVH需要输出连续的占空比波形来驱动后级mosfet,此时由于信号尾部的振铃叠加到后一个周期的占空比信号上去了,导致了后面对mosfet的驱动产生了干扰。

请问是否有办法滤掉尾部的振铃信号,续流二极管是否可以起到滤波效果?

DRVL的信号质量一直是比较好的,但是当负载变大后也会出现相位不稳的情况,估计是收到了DRVH信号的影响。

DRVH信号上的振铃如何去掉?

下图为轻负载下,DRVH上的尾部振铃。

另外在低负载下,DRVH的占空比是满足1.8/5=0.36的。

请各位TI工程师提供解决办法。

你好,由于我在国外,有时差,很抱歉不能给你及时回复。

关于轻载条件下尾部的振铃这是正常情况,因为在DCM模式下,下管是不导通的,所以当电感电流的di/dt发生跳变时,就会有ring现象产生。

你可以将重载条件下的输入电压波形截图一下么(务必)?谢谢

要减轻重载条件下的ring可以在下管加snubber吸收电路,电阻电容具体取值见附件

提供输入端5V的电压测量波形如下:

目前没有发现5V的输入端有问题或者压降,请参考

目前在轻负载情况小DRVH是非连续的占空比信号,随着负载的变大DRHV将会逐步缩小占空比信号之间的时间间隔,最终成为连续的占空比信号,

是这样么?

如果占空比信号已经联系产生,但是后级没有稳压到1.8V,那么DRVH和DRVL是会保持当前占空比还是会增大占空比?

目前提供了输入端的信号是否可以判断出问题原因了?

请问各位TI功能师,能否提供后续的测试思路?

另外TPS51216一共有几种工作模式?

D-CAP模式是指VDDQSNS在低于REFIN时打开上mosfet一个固定的时间,请问这个时间是2.5us*(1.8v/5v)么?

另外当负载变重后TPS51216是否会进入PWM模式,即输出连续的占空比波形?

如果发现输出的占空比波形不连续,时有时无意味着什么问题?

你好,

可以提供一下你的PCB layout么。

你的驱动波形发生震荡有可能是layout没有合理布局导致,

1, 输入电容要靠近芯片,

2,SW节点的面积要尽可能小

3, 最好是4层板, 一三层用来走信号线,二四用来屏蔽干扰

4, FB走线应远离高频噪声源,如SW

5, 输出电容应选取陷波频率在震荡频率附近的瓷片电容

6, 电流环路的走线尽可能短,以减小寄生电感

可以,目前是Cadence的allegro版本,可以么?

目前测试结果是在sw节点增加snubber电路,即可实现1.8V输出。

后续原因分析需要加强理论学习后总结。