UCC28950 带载到一定阶段后驱动抖动问题!

我正在进行UCC28950的3KW DC-DC的样件调试,遇到一些问题,需请教下TI的FAE ,

首先介绍下,工作条件:input 400-700V 输出 27V/110A;

我现在遇到问题是: 不加不同整流情况下, 加载到12A ,输出稳定,驱动稳定,但此时已移相到最大

占空比( 540V输入条件下), 再往上加载,COMP脚电压不变,驱动开始不稳抖动,是不是我的反馈环路有

问题,从0-12A的加载条件下 ,COMP上升,移相持续加大,未出现驱动不稳的情况 ,

现在持续加到30A,芯片保护,开始ss脚 打嗝重启了。请帮忙看下是什么问题导致的 。

此问题困扰我一个星期了,通过调整电压反馈参数未有根本改变,还希望高手能指导下!不甚感激

我的设计

变压器匝比:24:2 , PQ50

输 出电感: 2.0uH,

开关频率:100KHz

目前谐振电感: 6uH

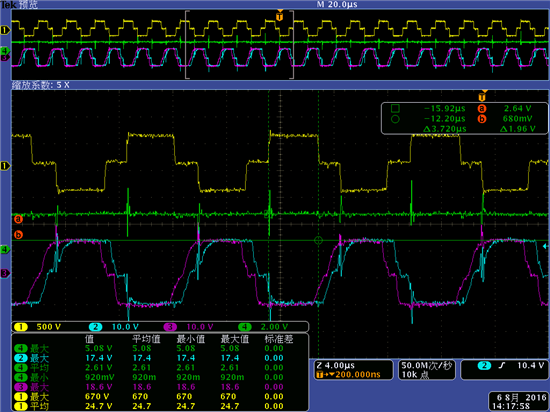

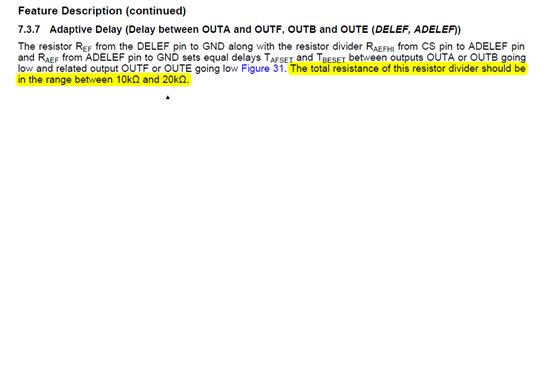

附件的为30A负载下 波形

CH2,CH3分别是 OutA OutD的Vgs, CH1: 变压器原边Vtx , CH4: COMP 脚电压

如下是30A 负载下波形

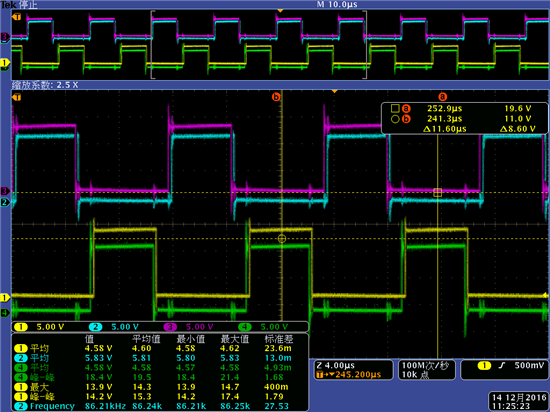

其中 CH4为 CS脚波形

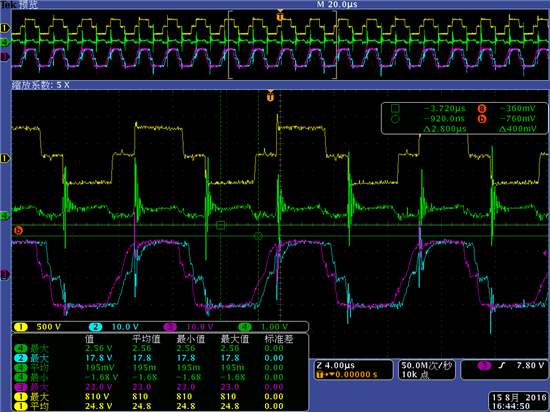

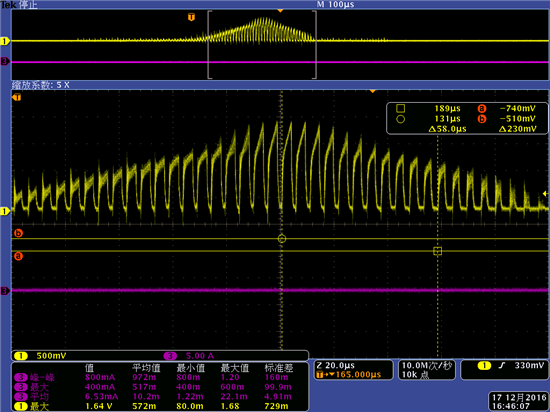

如下为 12A 负载下波形

您好,

能否把清晰原理图贴出来,方便大家一起讨论,谢谢~

Regards,

Patrick

您提到移相角到了最大值。请尝试提高输入电压,减少移相角试试。

CS上噪声太大,请确认是否为测试噪声,是否触发过流保护。

1、540V就达到最大占空比?说明你的变压器设计存在问题,你400V输入,27V输出,24:2的变压器是谁设计出来的?

2、SS端重启,说明IC受到了干扰,肯定是地线上出现了超过IC允许的负值的信号。

3、你应该首先重新设计变压器,然后改善PCB布局。

感谢您的分析回复,

我也怀疑是变压器设计有问题,所以重新设计的变压器如下

Np= (Vin_min -2* Vds_on) *Don_max_pre / (4*Bm *Ae* Fs)

其中 Vin_min= 400V , Vds_on= 0.8V , Don_max_pre= 0. 9 Bm=0.15T , Ae=328mm^2

Np= 23

匝比 Nt = (Vin_min -2* Vds_on)* Don_max_pre/ (Vo +Vf )

其中 Vo=27V , Vf=0.6V

Nt= 13

Ns= 2

还是 23:2:2

还有输出级用的是全波整流 。

请帮忙看下 设计有没有什么问题?

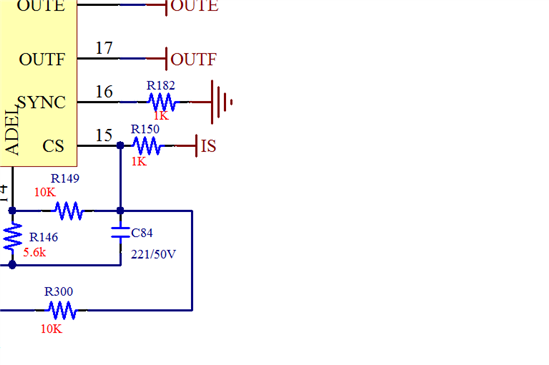

感谢您的回复, CS脚上的前沿尖峰很大, 会触发CS〉2V的过流保护, CS前端有加 1K , 220pF的RC滤波,好像没什么效果。

不知这前沿尖峰,是什么造成的,是Layout干扰吗?还是 漏感和 Coss的谐振? 如何降低其影响?

在不同输入电压下, 带载在0-10A下没有问题, 可再加载,我看到移相角已到了当时输入条件下的最大移相处,同540V 输入处, 是不是我的反馈环路有问题?

COMP脚上升太快,导致移相到最大?

如下是主功率板的原理图,请帮忙看看,分析下,在此多谢了!

- 计算没大问题,但考虑动态调整需要,最大占空比设计不能按0.9计算,推荐0.7~0.8.

- 在0到12A范围,应该是DCM模式,甚至burst mode,占空比随负载增加而加大。

- 关于测试的电流尖峰,请用地线环方法,排除测试带来的干扰。

是不是匝比导致最大占空比限制,可以提高输入电压试试,看可带是否负载增加。

感谢,Jason的回复,

变压器重新设计如下:

开关频率: 80KHz ,占空比 Dmax=0.8, Bm=0.15T , Vin_min=400V , Vin_max=700V , Vo=28V 计算

变压器变比 21:2:2

0-12A 时确实是占空比岁负载增加而加大的, 但超过12A负载后,占空比如何变化的,12A后,我看占空比已经是所在Vin下的最大占空比了,即 540V下,Dmax= 0.54 ; 这是什么原因,按照我的理解,应该是负载到满载时110A时, 占空比才到最大。 难道不是这样的?

还望指教,这问题困扰我好久?

还有关于CS 引脚的电压波形,在导通瞬间又很高的Spike尖峰,不知是什么原因,轻载时就有,还滤不掉,是不是布线干扰?

关于地线环方法测试电流尖峰,是怎么测试,我只是把普通10:1 的探棒,地线绕到最小,测试的,还有我有用电流勾枪测试原边电流波形,也是在导通瞬间有电流尖峰,这应该可以排除测试干扰吧。

您这儿所说的最大占空比是Dmax=0.54吗?

如果是,那就是正常的。CCM工作的全桥移相(属于Buck类变换器)的占空比不随负载电流变化,D=N*Vout/Vin, N为变压器匝比。

为方便理解,您可以看副边滤波电感前的电压波形,测量电压和占空比,两者乘积约等于输出电压。

感谢提点, 还有一个疑问, 你说 就是CCM工作全桥移相的占空比不随负载变化而变化,那负载的增加,全桥移相如何进行反馈调节的即表征到驱动占空比的匹配, 我的理解是负载从0 -〉最大负载,全桥移相角逐渐移相到最大,也就是最大占空比Dmax=0.54, 难道不是这样的, 还请指教,负载增加,全桥移相如何工作的,谢谢!

Jason,你好,感谢回复,经过不懈努力找到问题点,是驱动的问题,一经过调整,现在可以满功率带载了,

不过对于UCC28950的应用,还有些不明白的地方,想请教下,

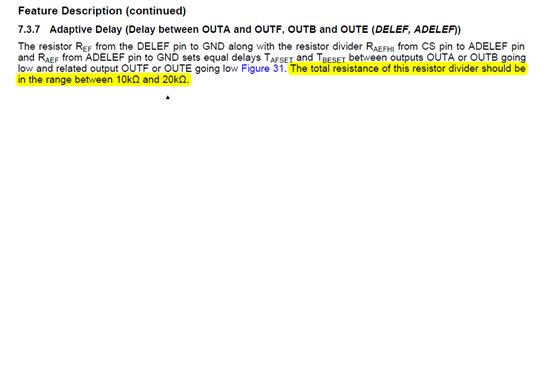

就是CS脚接ADEL和ADELF。自适应动态调整全桥驱动和同步整流的占空比问题, Application note 中计算是将Vref 接ADEL和ADELF分压的,计算出RA和RA(hi) , 那我现在接成CS脚接到ADEL和ADELF,那RA和RA(hi)电阻如何计算。我看规格书中写 ” RA+ RA(hi)< 20K ”, 这是什么原因,请指教一二,最终要的是CS接到ADEL时的动态电阻的选择,一直是困扰我的地方,谢谢!

感谢Jason的提点, 问题已经基本解决,目前已经可以带满载,不过对于28950的应用还有个问题需请教下,请帮忙看看,在此不甚感激。

我看规格书中写 ” RA+ RA(hi)< 20K ,是必须满足此要求下的值吗?

- 为避免不必要的麻烦,电阻值的选取请尽量遵照datasheet。

- DELEF、ADELEF等管脚都会从电阻分压网络中source或sink电流,合理的电阻值选择有利于确保各计算参数的准确性。

- ADEL和ADELEF管脚的电阻用于配置自适应时间范围,如果,分压电阻网络以VREF为参考,则相当于自适应功能没有用。delay时间长短跟负载无关。

- 如果分压电阻网络接CS pin,请参照datasheet中的公式(3)(4)(5)计算。delay时间随CS pin上电压变化,即随负载变化。

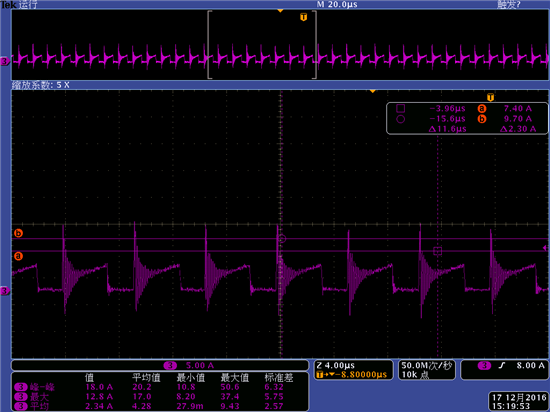

Jason,你好,感谢指导, 目前调试发现 28950的输出OutA,OUTB,OUTC,OUTD的逻辑时序为:

outD 超前OutA , OutC超前OutB, 这样设计的时候,超前桥臂 是不是 Out D, OutC,滞后桥臂应该是 OutB, OutA?

不是传统意义上的 OutA ,OutB为超前, OutC,OutD为滞后桥臂?还请不吝赐教。

如下为我测试的驱动波形,其中CH1-CH4 分别对应 28950的输出OutA,OUTB,OUTC,OUTD。

您好!

超前桥臂 是 Out D,OutC。

这个波形是在最小输入电压及满载情况下测的吗?貌似移相角很大,快到最大占空比了吧。

Jason,你好,

感谢提点,

所以在实际设计的时候 28950的 OutD,OutC 应该设计成超前桥臂,这样才能正确的移相工作吗?

不过我之前没注意把OutD,OutC设计成滞后桥臂,没加同步整流的情况也能带载正常工作,这样正常吗? 我的DELAB和 DELCD均设置为51k情况下。

还有我的驱动波形测试是在未通高压强电的情况下的控制板输出驱动波形,是移相角最大时的波形 。

您的全桥移相邮件参数基本一致(连死区都设置一样了),交换两个桥臂的控制也能工作的,实际中两桥臂的软开关程度不一样。

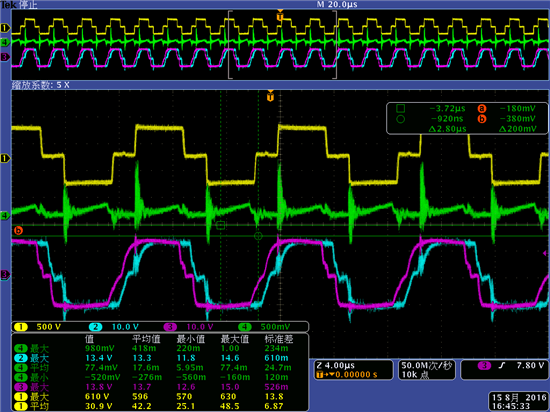

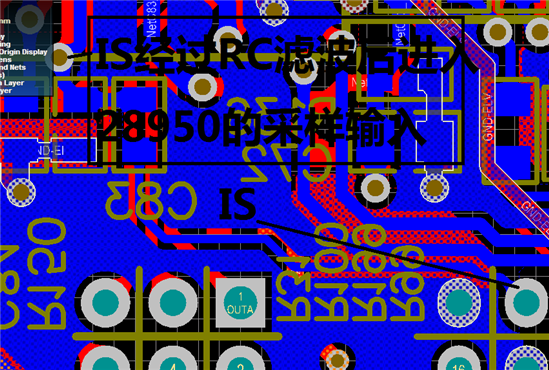

感谢Jason指点,目前还有个问题正困扰我,我的产品输出为27V的低压,B样机调试时,装有B样机的控制板,在带载到10A Load负载以上,UCC28950 的IS (电流采样)脚出现限流状况,波形如下图所示

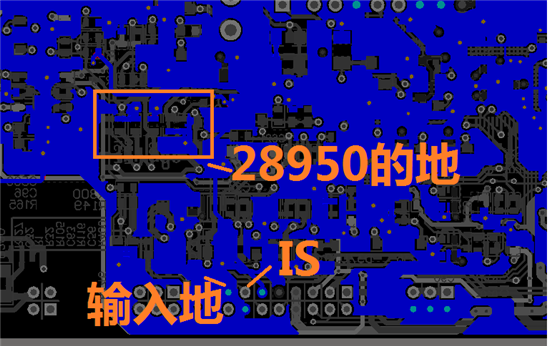

由于IS限流,导致控制不稳定,变压器等磁性元件吱吱响,这种情况,一直到我带载到30A,一直存在 ,超过35A 后,就出现输出电压掉电状况,不过只是把控制板换成A样件的控制板,进行带载调试10-25A略有响声,但IS电流波形正常,如下图所示, 过后一直可以带载到满功率110A ,未出现输出电压异常状况。

A样件和B样件的电压反馈控制一样,IS 电流采样一样,不知为何出现这种状况, 这样状况,是不是B样件的IS脚受到干扰影响导致的? A样件控制板和B样件控制板最大区别是铺地不太一样,如下是我的B样件PCBLayout,请帮忙看下这种状况是不是PCB Layout影响可能较大。

在此先谢谢了!

从波形看,不像单纯的IS pin受干扰,您再查查电路上其他地方跟A样机有没有不一样的地方,着重看反馈和补偿的地方。