TPS54340输入,输出纹波大

我用TPS54340照着它data sheet里的设计范例搭了这个3.3V-5A降压电路。然后在板子上实测输出电压稳定在3V,可以接负载。可是接了负载之后,输入、输出的纹波很大,有几百毫伏,而它data sheet里说纹波最大也才十几毫伏。我尝试着改变输入、输出电容,可无论并上大电容还是小电容,接负载输出纹波还是在500毫伏左右。

我测试时接的是5欧姆水泥电阻,用万用表测输出电压在2.99V。直流源供电9V,输出电流0.24A。

下面是各个引脚波形图

输出端交流耦合,峰峰值276mv,频率666kHz左右

输出端交流耦合,峰峰值276mv,频率666kHz左右

输入端交流耦合,峰峰值960mv,频率666kHz左右

输入端交流耦合,峰峰值960mv,频率666kHz左右

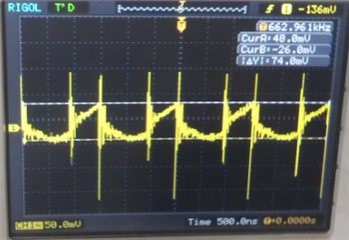

SW引脚,占空比1/3,方波频率666kHz左右;

SW引脚,占空比1/3,方波频率666kHz左右;

COMP引脚,频率666kHz左右,峰峰值74mv;

COMP引脚,频率666kHz左右,峰峰值74mv;

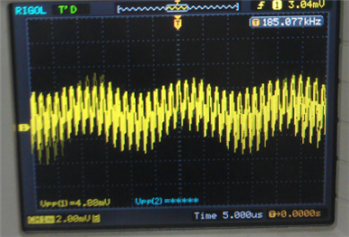

FB引脚,峰峰值232mv,这个频率好像比较低,200多kHz;

FB引脚,峰峰值232mv,这个频率好像比较低,200多kHz;

另外,我的EN脚直流1.8V,RT/CL脚直流0.5V,均正常。

我用的电感是7uH的,肖特基二极管最大电流3A(我知道有点低,但手头上只有这个,现在才输零点几安,应该不是造成纹波的主要原因)

麻烦大家帮我指点一下,为什么接负载后输入、输出纹波会这么大,电路应该怎么改进。

看你的波形,输出都是开关产生的高频纹波,不知道你输出接的多大的电容?可以试试贴片电容,或者LOW ESR的固态电容,再看看效果。

我输入接两个2.2uF电解电容,输出是接100uF电解电容。普通的电解电容不可以吗?

纹波大有很多原因,解决也有很多的方法,原因是你设计的问题。解决有把电感加大,还有把电容加大,当然还有后面直接并一个小的200K的电阻。最好的方法就是加大电容,另外再并一个104的小电容滤除高频的。电容不仅是容量,还要有耐压值。当然楼上说的也对,内部的电阻要很小。

建议加一级LC滤波来试一下。

建议输入接一个大容量电容,输出接高频电容。确保输入源没有限流。纹波测试探头可以并一个10uf的陶瓷电容看看。

再就是改一下环路参数,让环路稳定下来。

我后来先在输入并一个470uF的电解电容,发现输入、输出纹波都降下去了,但是它的高频尖峰脉冲有1V多,很难滤掉。波形如下

黄色的是输入,蓝色的是输出,除去高频部分,整体峰峰值在200mv左右。

我后来又加大输出电感和输出电容,电感用22uH,输出电容470uF,结果发现电感发出很大的响声,而且加负载输出电压往下掉,把大电容去掉后电感和输出电压都恢复正常了。

我现在是在输入加了3300uF的电容,输出用22uH电感和100uF电容,发现这次输入输出的纹波比之前好一点,除去高频部分大概有100多mv.波形如下

上面是输入,下面是输出,输入纹波有180mv左右,输出纹波有120mv左右。

上面是输入,下面是输出,输入纹波有180mv左右,输出纹波有120mv左右。

这种情况下还能再继续减小纹波吗?高频部分怎么解决,我尝试并104、103、1u、10u的电容,发现都没怎么变。

一般情况纹波是多少才是可以接受?

首先确定你的测量方法没有问题,(需要地线环,加高频电容)。

你这个基本都是高频纹波了,可以加LC,进行滤波,还有画板时候,要注意,避免开关噪声对后面输出的串扰。

一般来说1%输出电压的纹波都是可以接受的。

电感设计是否合理,包括感值和磁芯。目测电容esr对你电路的影响较大,可以拿几个电容并联,每个电容的容值可以适当取小一点。

遇到过类似情况。

规格书中介绍说纹波小,是因为布局等因素不用。

布局不好,引起纹波过大,不能怨人家芯片纹波过大。资料提的纹波很小,那是在他们设计的高质量产品中测量的。

直接用线搭接个电路,跟好好在PCB中布局, 肯定是不一样的。

嗯。之前的板子被我焊得乱七八糟,昨晚我又重新画了一次PCB,元件参数、布局等都尽量跟data sheet接近。板子腐蚀完后接示波器测试,纹波立马降到了50mv左右,而且波形比较稳定,输出只是接了220uF的电容,输入还是4.7uF,波形如下

上面的是输出波形,下面的是输入的波形。

上面的是输出波形,下面的是输入的波形。

后来我尝试着能不能把这50mv的纹波再减小,接了一级LC,结果发现无论怎么改变电容,输出纹波都变大了,变成90mv左右。想了半天,想起LIANGPING HU1会员说的“首先要确定你的测量方法有没有问题”,我就怀疑是不是我的示波器探头的问题,上网百度了一下示波器测纹波的内容,结果还真找到了一篇文章《总结示波器测量纹波》,网址如下

http://horatio.li.blog.163.com/blog/static/109246521201041551513905/

读完之后才发现原来我的示波器的地线接得太长了,于是我便照着文章介绍的自己做了一个接地弹簧套在示波器探头上

左边是自制的,右边是后来找到的原配的接地弹簧。再用这个测试时,纹波竟然直接就降到4mv了!连LC滤波都不用,加了反而增大了纹波,难怪我之前怎么都滤不掉纹波。。

右图是把时间轴拉长之后的图像。

之后又用这个带弹簧地线的探头测了其他引脚的波形发现都比之前的要稳定很多!这里就不一一上图了。

总结这次经验,在做电源芯片的时候PCB布局方面真的很重要,而且,尽量选择低ESR(等效串联电阻)的元件,更重要的是,测试方法一定要对!示波器探头的地线一定不能太长,不然的话,干扰会很大的。

最后,感谢 LIANGPING HU1 等众多TI技术论坛的工程师们提出的宝贵意见!

楼主,补充一点,你这里的图,SW波形上可以看到在高电平的时候,电压有降落,这就表明你的输入电容太小了,有些问题自己通过波形就可以去判断是什么原因造成的。输出的电压纹波由以下几部分组成:

1. 电流纹波在输出电容的ESR上产生的纹波,

2. 输出电容充放电产生的纹波

3. 输出电容的ESL产生的纹波,以及输出走线的线路寄生电感产生的电压尖峰。

有了以上的几点认识,你可以做出以下改进,输出电容改用ESR小的电容或者使用多个电容并联,减小ESR,另外输出电容走线尽量短而宽,减小线路寄生电感。

Hi

大部分这类电路中不会直接选择高ESR的电解电容,或者说至少要并联低ESR的陶瓷电容以达到降低ESR的目的,然后在确认环路补偿。

哇塞,发现myti的账户可以直接在这里登陆,真的很不错!

TI做的很好啦

Hi

注意输出电容ESR尽量低。