关于升压拓扑结构中的高di/dt位置的疑问

时间:10-02

整理:3721RD

点击:

各位TI的工程师你好

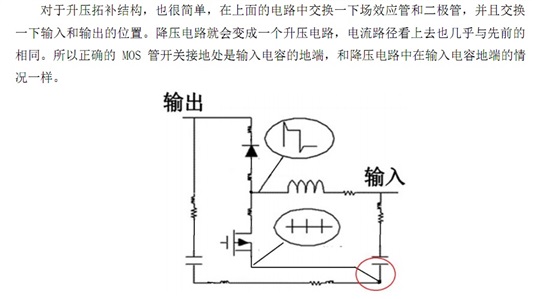

我在学习2013年8月版《德州仪器高性能模拟器件高校应用指南》的7.1.2节时,觉得文中关于升压拓扑结构的说明有误。

文中说正确的MOS接地处是输入电容的地端。

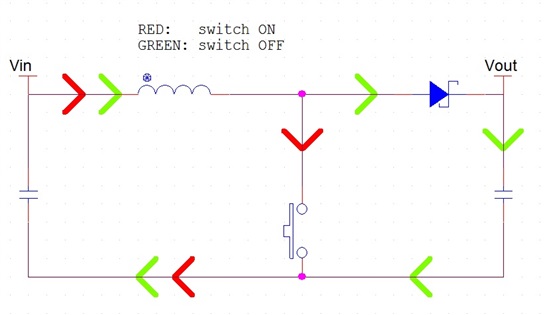

下面是我自己画的BOOST的电流情况,高di/dt回路是开关-二极管-输出电容回路,所以我认为正确的MOS接地处是输出电容的地端。

不知道我这样想对不对,请各位指教,谢谢。

你的图是画对了的。你看经过MOS的电流 Red是不是只回到了输入电容地?mos上流的电流没有经过输出电容。所以PCB布局的时候,MOS应该接在输入电容地上才能使Red电流流过的路径最短最优化。

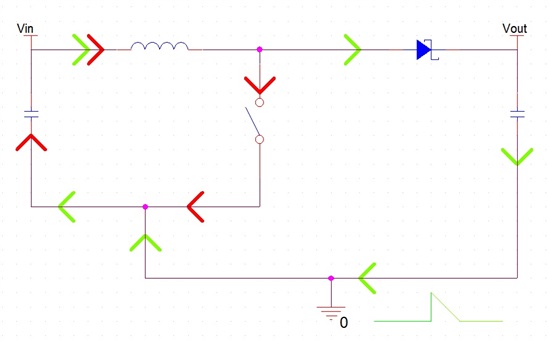

按照输入电容和MOS接我画了下图

这样的话,绿色电流的高di/dt会在地中产生一个尖峰电压的干扰。

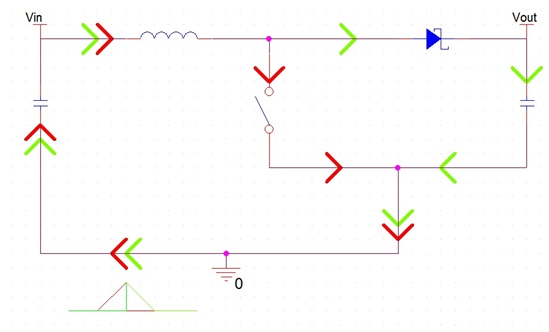

如果是输出电容和MOS接我画了下图

这样红色和绿色的电流先汇合,然后流入地,这样地中就不会有高di/dt电流了。

升压时高di/dt回路在输出电容上,降压时高di/dt回路在输入电容上

我也是这样想的,但是《德州仪器高性能模拟器件高校应用指南》中说高di/dt回路都在输入电容上,而且在后面章节的TPS40210EVM实例讲解中也是同样的说法。

我已经投了一个PCB,来验证哪种布局是对的。

BUCK是输入电流断续,BOOST是输出电流断续,我个人觉得你的理解是对的