LM25116几个波形产生原因

首先来张布局图(电路频率350K)

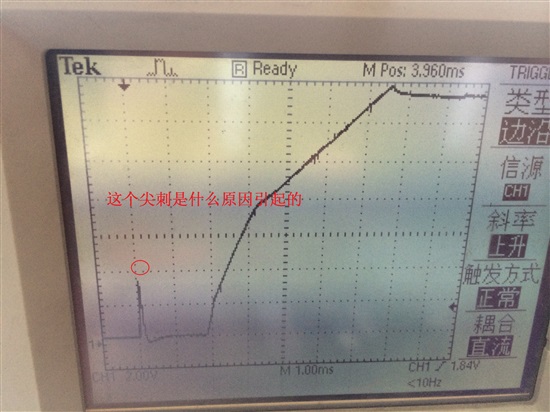

问题1

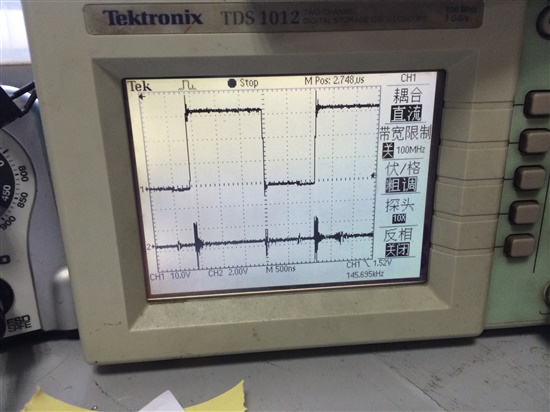

启动波形,负载液晶屏一块(屏参数12V,40W)

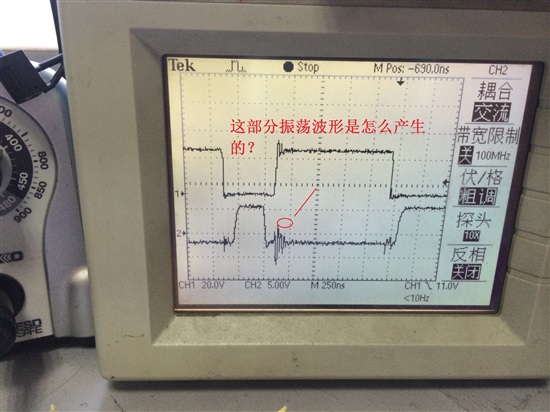

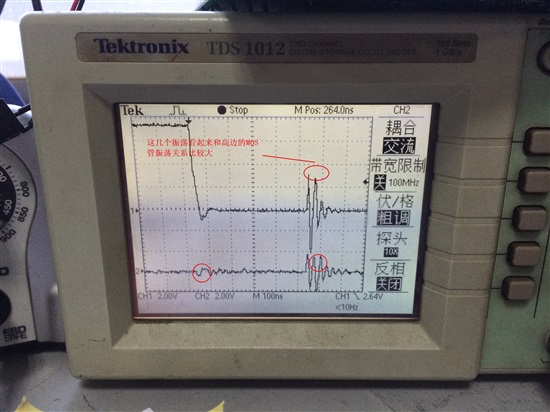

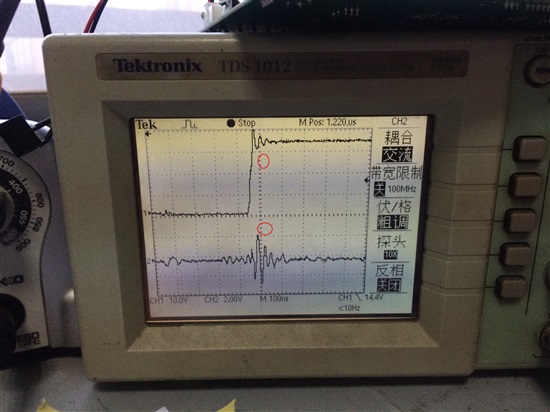

问题2

LM26116的高端和低端MOS管的驱动脚波形有个振荡,是什么原因引起

接上图说,在振荡的地方取样电阻上也产生同样波形,看现象像高边和低边的MOS管同时导通。下面3张是高边MOS管和低边MOS同取样电阻的波形。

问题3

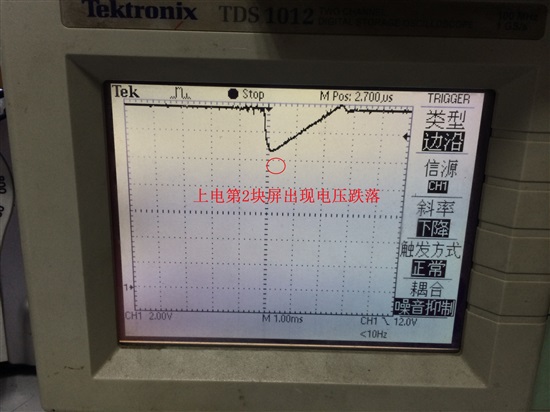

LM25116带负载,带2块屏(电压12V,40W),屏上电时序先1号屏,后2号屏,在上电2号屏时,出现一个电压的跌落。

亲,这是开关噪音。

开关的瞬间会产生一个尖峰

你好,这是DS电容充放电对GS电容的影响,所以驱动波形是在开关瞬间有振荡,谢谢。

是开关噪音干扰了。接下来有两个可能:

1. 干扰是真的。通过缩短测试探头的地线,依然能看这个尖峰,这就是真的了。消除办法是增大驱动电阻,或优化PCB设计。

2. 干扰是假的。通过缩短测试探头的地线,尖峰消失了。

Neil Li 你好!

可以肯定干扰是真的,对高边和低边的MOS增加栅极电阻,

做了以下测试,

1.在低边MOS管G脚串了个100R电阻,无法正常工作。(这个电阻还不能增加太大,不然出现不工作情况。)

2.在低边MOS管G脚串了个47R电阻,正常工作,干扰还在。

3.在高边和低边MOS管G脚各串了个47R电阻,正常工作,干扰还在。

PCB优化,能不能说下那些注意点。能不能提供下TI的demo给我们做个参考。

振铃很多时候是测试的问题,或者探头接地点的问题。

出现下冲是正常的,只要能正常恢复就行了。

Jason Shen

你好!

1.把示波器的地线做了剪短测试,还是有振铃信号。测试了多个接地点还是有同样问题。

2.我想知道是振铃是真的,怎么去做处理优化。

3.现在这样布局肯定不是最优,低边MOS管工作的时候,电感放电回路太长。但目前的结构MOS管位置是固定的,在现有基础上还能做那些优化?

4.如果把LM25116拆分成2颗异步DC-DC,有什么芯片介绍,最好是MOS管外置的。

自己给增加顶下,等待TI回复!

您好,

3.对于buck电路,可以在开关管的VDD和GND上并联一个低ESR,ESL的电容看看,注意使用尽可能短的线。

4. 你希望两路电源的输入输出分别是多少电压和电流?

亲;看样子,你还没理解这个毛刺。建议仔细阅读一下MOSFET数据表。请特别注意Qdg这个参数。

对于这个毛刺,在开关电路中是必然存在的,是由栅漏极间电容耦合而成。只要漏极有电压变化,栅上就会耦合对应的波形。它只有大小变化,没有有无问题。改变测量位置也无法掩耳盗铃。

您好,我想问一下,我用LM25116做了一个24V/12V的,但是没与输出,而且芯片16脚的VCC没有7.4V的电压,这是什么原因造成的?谢谢

问题1,看一下在那个瞬间,是否有其他电路启动了,可能是干扰

问题2,耦合过来的开关干扰

问题3,按理说输出电容有1000uF,40W负载不应该有这么大的电压跌落。可以看看此时负载电流是否真的很大,是不是带宽也可以提高一些来解决