3D封装对电源管理器件性能及功率密度的提升

PDF 版下载链接: http://www.ti.com/cn/lit/zhct305

引言

自出现以来,半导体产业一直遵循着资源最大化的轨迹。持续收缩的工艺技术使得芯片设计者可以集成更多的创新技术到更小尺寸的晶元上。而亚微米工艺的引入从空间上反向影响了芯片设计领域:虽然芯片的物理面积不断缩小,但是芯片设计者可以操作的空间变大了。

现在,这个行业面临着物理学定律的挑战。继续减小晶元的工艺尺寸并不能相应带来同等的性能增加。当然,市场对芯片性能提升的追求是永无止境的。特别是高端计算机和通讯系统,对电源管理器件和其他类型芯片高性能的要求与日俱增。

许多力量在推动芯片设计人员去寻找和发现包括芯片封装在内的半导体产业创新。一个芯片如何被封装甚至和芯片本身一样,对电源管理器件的性能参数至关重要。一个芯片的性能不应该止于封装;相反,如果一个芯片已达到其最大特性,封装可以增强和延伸其性能。

创新的芯片封装技术和芯片本身一样,对整个芯片的性能参数至关重要。这适用于许多电源管理器件应用的领域,如高性能计算机,通讯系统。在这些领域中,效率,尺寸,电流能力,热管理和稳定性最为关键。

比如,提升通讯设施里交换机,服务器,网关和其他系统里DCDC变换器的效率可以降低系统的功耗,从而降低供应商维护操作基础设施的费用。还有很多其他的例子来说明电源管理器件特性的重要性。器件的封装技术,包括从2D到3D的变化,对芯片的性能优化起了主要作用。

TI的Powerstack™封装技术是一种简单且独特的3D封装方案,它在许多应用和系统里提升了电源管理器件的性能参数。本文会着重介绍Powerstack™技术的优势,实际应用结果以及在未来的发展前景。

1 新维度上的创新

在过去,设计一个系统的电源子系统时,需要找到性能合适的器件并有效的使用它们。但对今天高性能计算机和通讯系统的需求来说,设计一个电源子系统非常具有挑战性。多路且相当多样化的电压需求,体积的限制,环保材料的需求,更低的功耗以及其他的考虑会影响到电源系统的设计和组成。

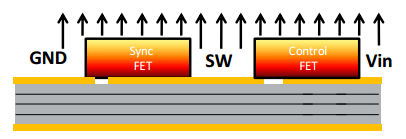

比如, 由于系统环境的改变,DCDC变流器的设计也相应的改变。对手机市场低端低电流的应用,单晶元的方案或者双晶元的方案(包括一个控制器和MOSFET)可以满足大部分的需求。如果需要额外的MOSFET,通常放在第一个MOSFET的旁边并使其内部连接到控制器。这种两个MOSFET 并排放置的方式消耗了明显的板面积;同时,因为芯片之间的电寄生参数,影响了变流器的性能。(如图1)

图1. 两个MOSFET和控制器IC并排放置的方案

2 叠层放置MOSFET的好处

为了克服分立方案的不足,TI发明了Powerstack™封装技术。不局限于两个维度,Powerstack™封装方案利用三个维度,把MOSFET堆叠在一个创新的封装里。和其他封装技术类似,堆叠的主要好处是充分利用了3D的集成度。堆叠技术减小了芯片的2D面积,并节省了板空间。当然,Powerstack™封装除了节省空间,在其他方面也有一定的优势。

Powerstack™封装的额外优势是增强了电性能和热性能。如上所述,堆叠方式通过公共点的直接连接消除了一些电寄生参数。Powerstack™封装中的铜片连接是一种非常有效的技术,它可以充分的利用封装技术并提供非常低的阻抗。同时,TI的NexFET™也很适用于堆叠技术,因为其地端可以和封装的散热片连在一起,更有效的把热传递给印制板。Powerstack™充分利用了各种封装技术和材料,可以实现更多的集成。

TI NexFET™同步BUCK功率模块是一个典型的堆叠封装实例,它把两个MOSFET集成在一个小外形封装内。再在同样的封装内加入一个控制器就构成了完整的功率控制部分。

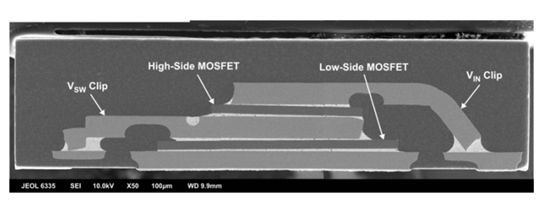

图2. 使用Powerstack™封装芯片的横截面

一个利用Powerstack™技术制成的功率模块芯片横截面如图2所示,其中上管MOSFET和下管MOSFET通过厚铜片连接起来。下管芯片和引线框的基板连在一起,同时也为下管的地提供一个通路。这种结构可以给电源子系统的设计人员带来很多好处,比如节省了布板空间,提高了电流能力,效率和热性能。

2.1 节省布板空间

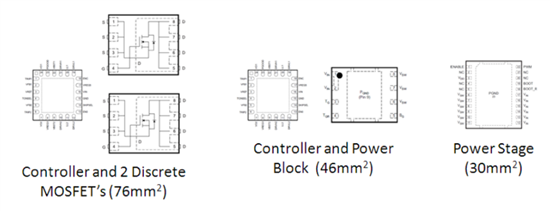

在今天,由于高性能计算机和通讯产品越来越小型化,故减少布板面积非常重要。而3D封装的创新为这种减少提供了可能。和之前几代封装局限于X和Y维度不同,Powerstack™可以充分的利用Z维度。与分立的MOSFET相比,把两个MOSFET竖向组装在一个封装里,可以节省同步BUCK变流器至少一半的面积。如果把控制器再集成在相同的封装里则更进一步节省空间。因为Powerstack™封装的灵活性和扩展性,通用的控制器都可以被集成,一些满足特殊应用的客户化解决方案也因此容易被开发。

图3. 使用Powerstack™节省布板空间的实例

2.2 更高的过电流能力

图4. 使用Powerstack™可支持更大电流和更高开关频率

图4的电路显示在Powerstack™封装中芯片的电寄生参数非常小。在此种情况下,寄生电阻和电感的幅值及出现概率都减小了。因此,由于导通损耗和开关损耗的降低,芯片过电流的能力被增强了。在电源系统中,高速的开关频率因其显著减小外置电感的大小和价格广受青睐。而使用Powerstack™封装,可使用更高的开关频率,为布板空间的进一步减小打下了基础。

2.3 效率

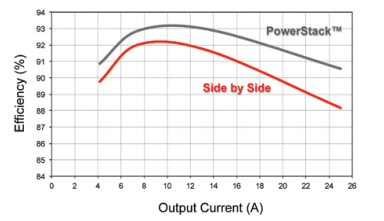

Powerstack™封装可以减小电路中的电寄生参数,从而减小了开关和导通损耗。所以,与分立解决方案相比,可以实现更高的转换效率。图5是Powerstack™封装和普通分立封装的效率曲线比较。

图5. Powerstack™和离散方式的效率比较

2.4 热管理

Powerstack™的另一个优势是热性能。如前所述,此种封装可以显著降低寄生的电参数,所以可以降低开关和导通损耗,从而产生更少的热损耗。在高性能计算机和通讯系统中,降低功耗可以节省能源和散热的开支,且把预算留给高性能的DSP和处理器,故降低功耗是最重要的设计目标之一。

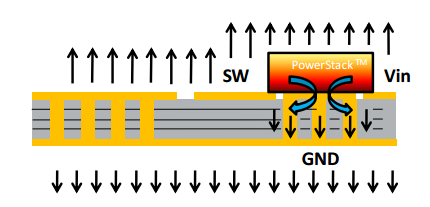

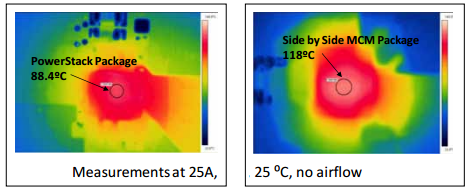

图6. Powerstack™封装通过地平面优化的散热路径

同时,Powerstack™本身的结构也可以提升热性能。在Powerstack™封装中,封装底部的焊盘一般是和地连接在一起的,而通常,在系统中地层是最大且最容易导热的平面。所以,Powerstack™封装利用热传导路径对热性能进行了优化,如图6所示。相反,传统的分立MOSFET或者并排放置的MOSFET一般被置于开关节点或输入节点。而这些节点并不像地平面一样容易散热。从图8可以看到两种方式热性能的显著差别。

图7. 传统分立MOSFET散热路径被SW和VIN节点限制

图8. Powerstack™和并排放置MCM的热性能比较

2.5 稳定性

在电源管理的封装中稳定性是一个重要的需求,通常被放在很高的优先级里。Powerstack™封装技术的稳定性在功率模块和全集成产品里被广泛验证,满足或超过了TI的质量,耐久性和可靠性测试。而Powerstack™的散热能力又提升了芯片的稳定性,它可以显著降低器件生命周期的操作温度。

3 封装的作用

TI的Powerstack™封装技术显示出芯片的封装在半导体芯片的性能和具体参数上具有关键作用。特别是在同步BUCK变流器的功率模块里,Powerstack™显示出这种新的3D堆叠创新可以帮助优化电源管理器件的重要参数,包括布板面积,效率,过电流能力以及热性能。在高性能计算机及通讯设备等许多应用中,Powerstack™可以极大提升系统的性能并降低终端产品的风险。此种技术会在将来广泛应用。

更多的信息,请访问 www.ti.com/powerstack

感谢分享