3138程序PWR027中Edge Generation和主从同步是否冲突?

时间:10-02

整理:3721RD

点击:

在PWR027程序中有如下语句:

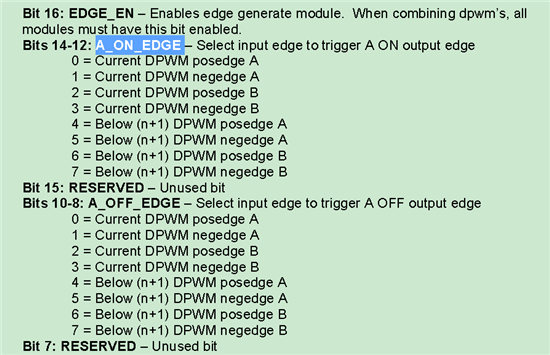

Dpwm2Regs.DPWMEDGEGEN.bit.A_ON_EDGE = 2; Dpwm2Regs.DPWMEDGEGEN.bit.A_OFF_EDGE = 5; Dpwm2Regs.DPWMEDGEGEN.bit.B_ON_EDGE = 6; Dpwm2Regs.DPWMEDGEGEN.bit.B_OFF_EDGE = 1;

这个用在这里主要是什么作用?

和主从同步是如何协调的?是否有冲突?

LoopMuxRegs.DPWMMUX.bit.DPWM3_SYNC_SEL = 2;//DPWM3从于DPWM2

是选择哪一个通道的上升沿或下降沿去trigger当前通道的ON或者OFF。

通常用于移相全桥拓扑中。

我想问的是先后问题,就是Dpwm3 从于DPWM2,这个DPWM2是EdgeGeneration发生之前的DPWM2波形 还是之后最终输出的DPWM2波形?

DPWM2 Edge中选择的DPWM3A的下降沿 是 从于DPWM2后生成的 DPWM3波形还是 事件生成的DPWM3波形“?

我想问的是先后问题,就是Dpwm3 从于DPWM2,这个DPWM2是EdgeGeneration发生之前的DPWM2波形 还是之后最终输出的DPWM2波形?

》》》》》这个DPWM2是EdgeGeneration发生之前的。因为同步使用的trigger信号是源于DPWM2模块。

DPWM2 Edge中选择的DPWM3A的下降沿 是 从于DPWM2后生成的 DPWM3波形还是 事件生成的DPWM3波形“?

》》》》》从于DPWM2后生成的。

请教下,这个东西如何和移相全桥配合使用呢,能否说得具体点,或者举一个例子呢?

谢谢!

如果我Dpwm2Regs.DPWMCTRL0.bit.CLA_EN = 1; Dpwm3Regs.DPWMCTRL0.bit.CLA_EN = 1; 和这个会有冲突吗?

谢谢!