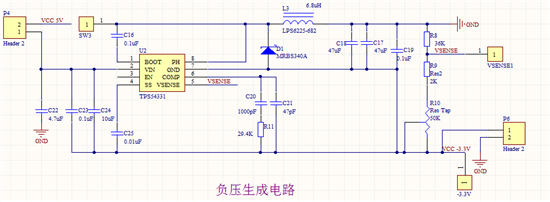

关于tps54331负压生成的疑问

时间:10-02

整理:3721RD

点击:

我网上找到了一个负压生成电路,原理图如下,理解了原理后,做出来使用了,感觉效果还不错,但是根据tps54331芯片数据手册的数据,有点小小的疑问,希望有人指教一下:最大负压输出达到-15V时,测VSENSE处的电压时,发现电压有-14.17V,可是芯片手册上说这个引脚的电压时-0.3到3V,所以有疑问,这样不会烧坏芯片吗?

你的原理图输出不是-3.3V吗?

datasheet给的这个数据应该是相对芯片的参考点电压,负压输出应用参考点显然是输出的低端电压,所以还是在范围内

可以根据R10那个电位器调压,最大输出15V左右

参考点不是地吗?有点不明白了

不是;这里是以输出为参考地。

不论哪种拓扑结构,芯片内部的逻辑部分和引脚的耐压,都是针对芯片本身的GND引脚电压来做为参考的,在做反压变换器时,芯片的GND是连接在输出的,也就是-15V。那么VSENSE相对芯片GND的电压实际上只有0.83V,并没有超出引脚的耐压范围。

原来是这样 。。。明白了