TPS53353总是不断关断重启

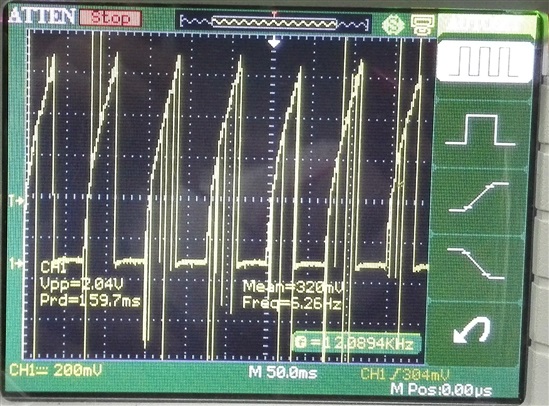

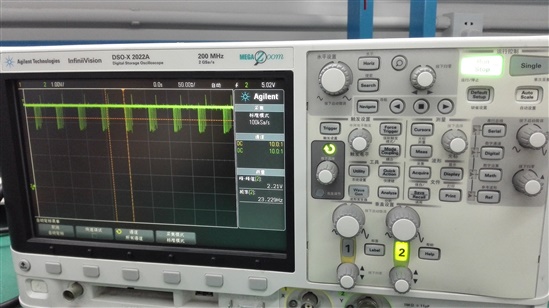

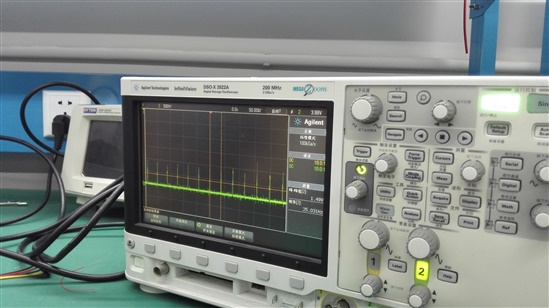

之前提过关于TPS53353问题,详见http://www.deyisupport.com/question_answer/analog/power_management/f/24/t/76634.aspx。目前遇到新问题如下:TPS53353的输入为12V,10A的直流,输出端LL引脚的波形为

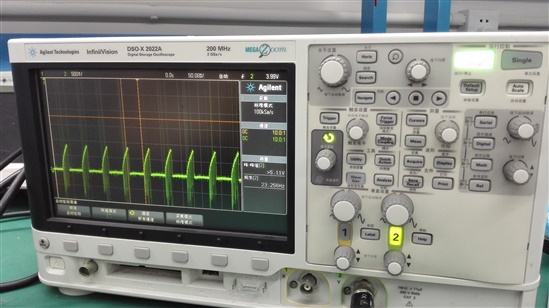

这个波形与其datasheet中的过流保护有类似,可是我并没有加负载,检查过输出并没有短路后,我测试了一下VREG波形如下:

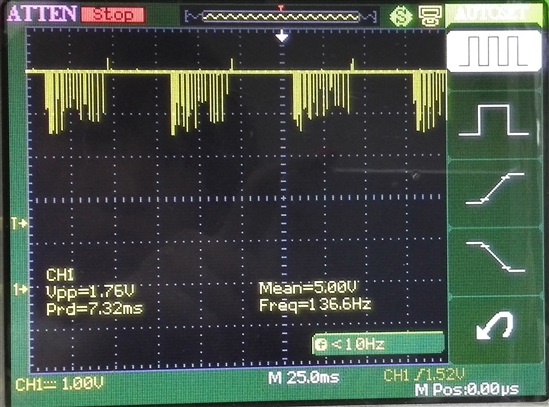

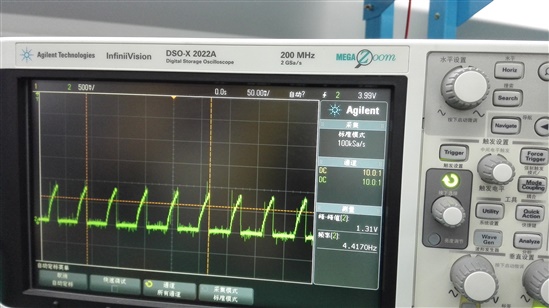

发现该电平每隔大概75ms就会有一些明显的下冲,使VERG低于其关断阈值3.95V,此时,测试PGOOG端的波形如下:

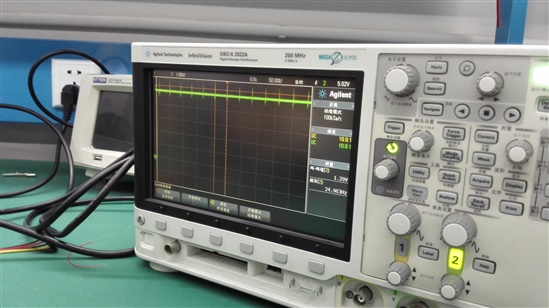

看到也是大概每隔75ms就会有一个脉冲,我几乎可以肯定是内部的LDO在产生5V的VREG时出了问题,测试VDD的输入(和VIN一样的12V),波形如下:

难道是芯片本身的LDO有问题?我已经换过芯片了,这个问题依然存在,求高人指导!

自己顶一下,我尝试过在VREG端加一个100uf的钽电容滤波,VREG倒是没下冲了,但是输出电压也测不到了。求高手指点!

可否上传PCB截图?

你好,EN波形上传下,谢谢。

你好,原理图和PCB截图在之前发的帖子里面有,详见http://www.deyisupport.com/question_answer/analog/power_management/f/24/t/76634.aspx。

Frank:

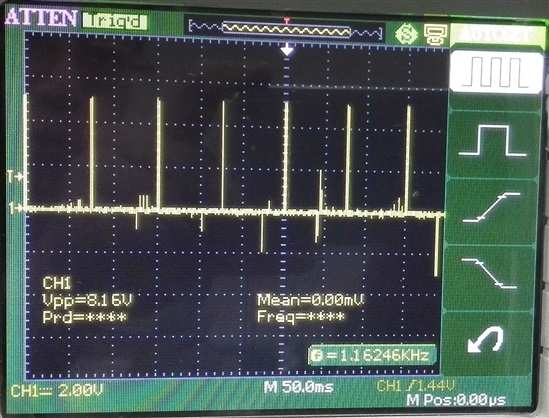

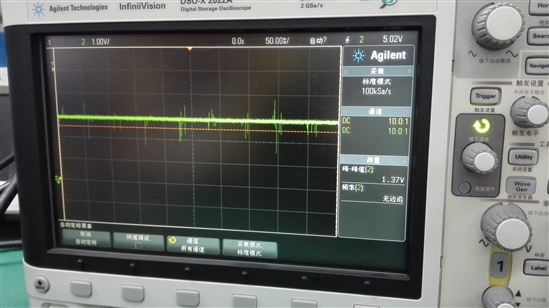

你好!由于用了一台精度更高的示波器测试,我把最近一次的波形一并贴上如下:

EN:

VREG:

LL:

output:

我尝试过用一个22uf的钽电容给VREG滤波,过后的波形如下:

vreg:

output:

en的波形基本没有变化。我把VREG和BUCK的OUTPUT波形放到一起比较,发现在VREG有下冲的时候,VOUT才会有一个斜坡波形,末尾VREG出现一个过冲的毛刺时,VOUT就掉下去了。这一点我一直都十分不解。麻烦Frank帮忙看一看!

哪里受到干扰?

你好,我怀疑你现在的问题就是因为pcb布线太细的原因,谢谢。

您好,我也怀疑过。因为VREG有周期性的过冲和下冲,频率也不高,比市电频率还要低不少。换不同地方测试也存在一样的问题。检查PCB走线,VREG在片外一个是给PGOOD供一个上拉,另一个就是选择芯片开关频率。我把上拉去掉,选择默认开关频率,VREG的波形几乎没有任何改善。VREG通过内部的LDO产生,供电的VDD是12V,完全不存在这样周期性的毛刺。EN通过12V分压而来,也基本不存在周期性的下冲。或者是我没有注意到其它形式的干扰?您有什么建议么?

您好,我把6个LL输出都串起来,然后通过一条挺粗的镀银线接到BUCK的输入端,再进行测试,几乎没有任何改善。这样做可行么?如果可行那输出没有改善是不是说明有其它的原因呢?谢谢!

Frank:

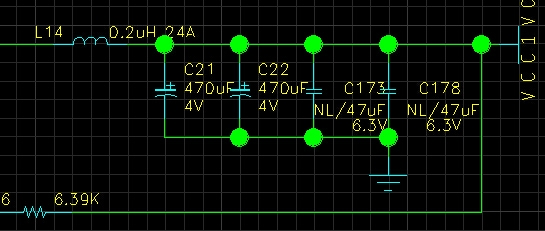

你好!你觉得如下的输出LC设计有问题么?

谢谢!

问题解决了,最终发现是接地的原因。原理图中,我把芯片中间的P-PAD接到了模拟地,芯片的其它外围引脚接到的是数字地,两个地之间通过一个磁珠隔离。示波器测试发现,数字地波形较好,而模拟地上面则有周期性的毛刺,其周期恰好和输出端的锯齿波形吻合。我把两个地短接之后再上电,之前存在的问题就没了,电源输出良好。