关于LDO并联可行否?

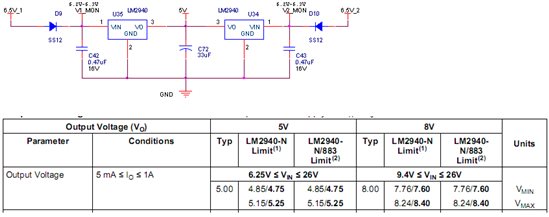

如今要实现冗余电源-》5V,0.5A,现在使用LDO芯片LM2940S-5.0/NOPB并联实现,

1、6.5V经过二极管变为6.2V,经过LDO会实现5V输出,这种冗余电源实现可控电源方法可行否?

2、我将LM2940改为LM1117 5V输出是否也是同样可行?

3、在固定负载下,两片LDO芯片是否均衡输出,与VIN无关。

两路电源不会均衡输出的。

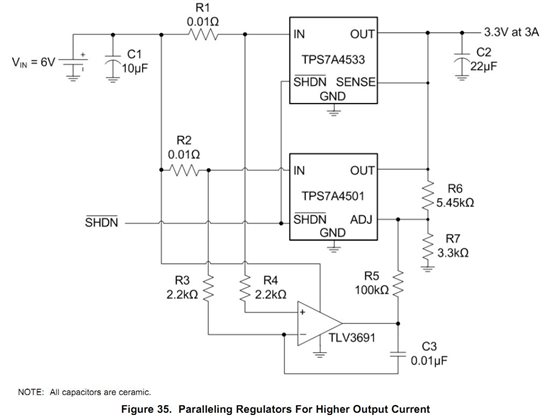

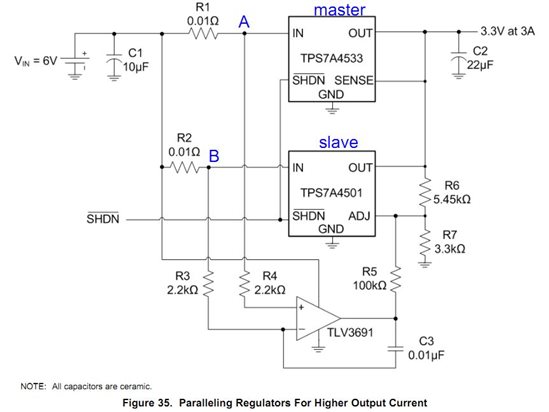

要把LDO并联起来的话需要额外加一个运放来分别采样LDO的两路输入电流 然后反馈到其中一个的FB引脚,才能完成电流的平衡。

近期会有关于LDO并联使用的文章推出。

如果推出了我会贴出来给你的。

OK,不会均衡输出我认可了,那么其他两个问题的答案呢?

这样的接法会不会损坏LDO芯片

这种接法不会损坏LDO,只是让两个LDO之间的电流差异很大。

如果负载过大,会导致LDO过流保护。

不推荐这么使用,LDO并无均流机制,谢谢。

负载我选择是单个LDO可以承受的负载,这种接法只是为了实现冗余电源输入,稳定的5V电源输出

仅仅为了冗余应该是可以的,考虑如果不均流,一个电流比较大90%以上,一个电流小10%以下,如果电流较大的坏掉,相当于切载了,电压跌落大小和时间在可接受范围内即可,我的理解是这样,欢迎补充指正。

这种方式,不一定能得到期望的结果,因为LDO如果损坏,你要看他是如何坏掉,如果是断路还好说,如果是短路呢?

不会均衡输出

但是这个LDO在你这种应用下可并联

原因是你的负载时0.5A,而单一LDO输出能力是1A,所以没有问题

作为热备份和冗余,这么接没问题。注意散热即可。

要把LDO并联起来的话需要额外加一个运放来分别采样LDO的两路输入电流 然后反馈到其中一个的FB引脚,才能完成电流的平衡。

要把LDO并联起来的话需要额外加一个运放来分别采样LDO的两路输入电流 然后反馈到其中一个的FB引脚,才能完成电流的平衡。

也可以加另外均流控制IC来做控制。

建议用电源管理的IC去实现多电源的管理。虽然增加了些成本,但可靠性可以保证。VICOR的一些技术可以实现冗余,可以参考一下。

LDO是可以并联使用的,但是一定要注意两个芯片的均流特性;

一般只要把均流做好的话,是完全可以并联的!

均流是关键。

LDO芯片一般输入要大于输出2V以上,也就是说输出5V,输入最好要大于等于7V;

知道了,谢谢

可以设置成主从模式,正常情况下,主模块起主要作用,从模块辅助。当主模块故障时,从模块继续工作,实现冗余设计。

一般的LDO电源不建议并联使用,因为无法保证均流,容易损坏,VICOR电源就可以,因为有做这方面的处理。。。

LDO并联肯定是没有问题的,你只要把并联的几个的LDO均流的技术搞定就可以啊!

LM2940改为LM1117 5V这个试试就知道啦,我没用过LM2940,不好帮你了。第三个问题我觉着应该能均衡输出的吧,vin不一样的时候,电流也不一样就行呀!

输出的均流看你要用什么样的方案去做了,接两个二极管也能做均流!

本身无法做均流的话,我们还可以借助外部的电路或者器件去实现均流功能。

LOD的电源不建议并联使用,因为LOD简单的电源无法做到均流,特别是电流比较大的时候,电流大的就会越来越大,导致这路加剧损坏。

求推荐:集成一路3.3V LDO和一路1.2V DCDC的芯片

| LDO芯片种类是很多,但楼主要求一个芯片集成一路3.3V LDO和一路1.2V DCDC的芯片,这类IC估计没有,楼主还是用两芯片吧,先LDO输出3.3V,然后再用一个芯片转成1.2V. |

每个LDO比较器钱都是分压电阻和基准电压比较,那么基准电压谁来提供呢?

LDO内部自带的,你可以看下LDO的内部结构图···

TPS65320 - 40V Step-Down Converter and LDO Regulator

你好

可以看看以下链接,纯粹为解决你的问题,但是感觉并不必要,电流不够可以用开关电源,需要冗余可以参考服务器上应用加ORING控制器。

http://blog.sina.com.cn/s/blog_628dd2bc01013qxe.html

加个电阻可不可以?

有帮助,依然不能保证均流。

Hisen 你好!

请问TI是否有LDO并联使用的相关文章?我现在使用TPS7A4700,想用两片并联(用运放均流)使用以减小每片的发热。

多谢!

你好,不建议LDO并联使用,谢谢。

Frank你好,

能否具体描述不建议LDO并联使用的原因是什么?据我所知LDO通过运放均流是有可能的,见TPS7A4501手册的figure 35。我想知道TPS7A4700是否也能这么用。如果不行,有没有和TPS7A4700性能接近(主要是PSRR)但热阻小一些的芯片?现在问题主要是一片4700计算下来的发热过大,单一负载,只能想到并联LDO并均流,来分担热耗散的办法。

您好,关于并联

1. 单路LDO输出5V,外接一个大于5V的电压(例如5.5V)在LDO输出端,此时LDO会吸入一个小电流,如果这个吸入的小电流可以接受,那么就可以并联。

2. 均流,串联小电阻均流是最简单的方式,当然也可以使用反馈来均流。

3. 如果仅仅是为了冗余设计,可以采用o-ring实现并联。

谢谢

Jason 你好!

我的应用不是为了冗余设计,而是分摊热耗散。1片TPS7A4700的热耗散太大,想用两片并联均流来降低芯片温升。

你说的第一点,我也在考虑反灌电流的问题,但是从TPS7A4700手册上看不出LDO能吸入多少小电流而不损坏。请教,这个吸电流的能力体现在哪个参数上?能否帮忙确认一下TPS7A4700是否能够用运放均流?谢谢。

另外,我看了TPS7A4501手册中的参考图Figure35,电路原理是对的,但分析过程似乎有问题,尤其是这一句:In the case where the TPS7A4533 is sourcing more current than TPS7A4501, the comparator output will go high。从图中看,master电流升高时A点电压应该下降,低于B点电压,则运放输出应该为Low。而且,图中R5是否应该参与slave反馈节点的电压计算,我表示疑问。请TI工程师查证一下。谢谢!

附TI官方另一款LDO均流开发模块:http://www.ti.com.cn/tool/cn/tida-00270,供参考,可惜的是里面没有详细描述运放输出端电阻值的计算,只是给出了15K的阻值。

你好,LDO散热不够的时候可以考虑使用buck 降压再加LDO的方法,谢谢。LDO并联不是不可以,不建议是因为不常用,谢谢。

也要实现均流?

YES

Hi

用一级DC/DC降低LDO输入输出的压差,然后在选择一个输出电流较大的LDO.

Hi Johnsin,

采用TPS7A4700是因为其良好的PSRR(此参数优先级最高,要求在50db以上,10MHZ以内)。目前电源架构是这样:12V输入,经过TPS54521 buck降压(DCDC的输出可连续调节),再进入TPS7A4700,最终使得LDO输出电压在0.5~8V连续变化。max电流1A。

根据TPS7A4700手册figure17,在Vout较高时,如Vout=8~10V,其1MHZ点的PSRR会严重下降,只有30多db,需要提高压差来提升PSRR。若取ΔV=2V,则4700的温升将高达60多度。单一负载,不能使用两片LDO分离供电,所以考虑LDO均流。

如果您有更好的方案,请推荐。谢谢!