关于TPS54325的建议补充

时间:10-02

整理:3721RD

点击:

1.问题描述: iSee 提出问题:“我们在当前的设计中遇到了 IC 控制器的温度问题(高温)。对于如何在通用的同步降压概念设计方案中提高 IC 控制器(集成开关)的散热效率,有人可以提供建议?”

2.原文链接:http://www.deyisupport.com/question_answer/analog/power_management/f/24/p/128/256.aspx#256

3.解答问题的TI FAE: Weilin Chen

4.个人的收获:

原帖的楼主发帖咨询了如何能提高散热效率。

我结合自己使用该芯片的情况,也谈谈自己的看法。并且针对该芯片在使用过程中遇到的另一个问题,也通过此帖发表一下。

Weilin Chen 给出了自己对该芯片提高散热能力的建议“TPS54325 已经采用了带散热焊盘的大型封装,因而如果板面布局合理的话,散热应该不是问题。您能否将您电路板的板面布局图贴上来?您希望它工作在何种温度条件下,以及环境温度是多少?

有两种方法可以降低工作温度,一种是减少功率损耗,另一种是降低对环境的热阻。

要降低功率损耗,您应该选用另一种不同的部件。TPS54320 采用了较低的 Rdson FET 和可编程开关频率技术。较低 Rdson FET 可降低满负载功率损耗,而降低频率则可以降低所有负载的损耗。另有效率更高的器件 TPS54620,其采用甚至更低的 Rdson FET。

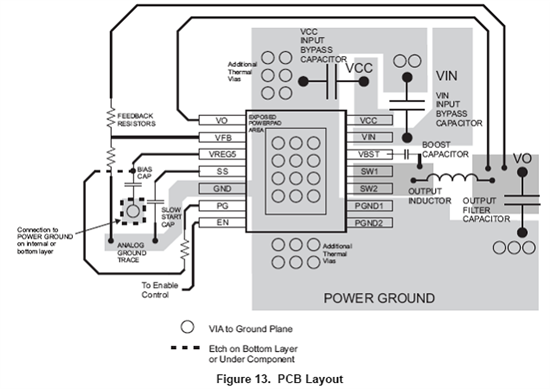

要降低热阻,您需要增加散热焊盘所接触敷铜面的面积。使用器件下面的通孔将顶部的铜面与电路板的所有各层连接在一起。同时尽量增大接地层。”

ti.com/thermal 上有大量相关信息,我建议您阅读一下。”

针对散热问题,也谈下自己的看法:

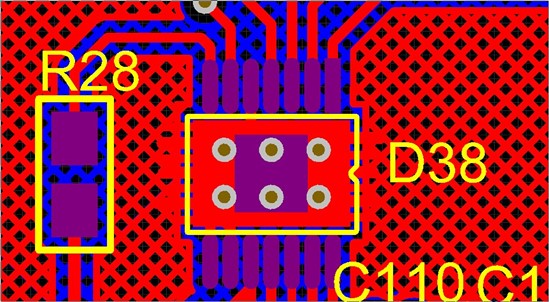

1. 个人使用过TPS54325芯片,感觉首先最重要的是要,保证该芯片的焊盘与PCB的焊盘充分接触,这样才能保证散热,从而能提供足够大的电流。如果只是通过小过孔将焊锡流进去,效果就不是很理想。甚至出现长期带不动稍微大载的问题。

如上图,中间那个大焊盘,一定要保证充分焊接到PCB板上。

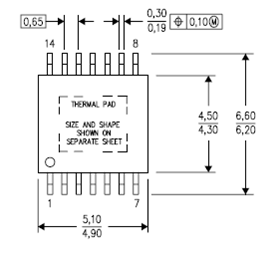

2.参考规格书中的介绍,见下图:

散热面积要保证足够大,而且增加一些过孔,有利于散热。

3.空间大的话,考虑连接焊盘的部分区域不弄绿油,上锡,有利于散热;

布置多层板,通过将热量引入到厚的铜箔中去,也有利于散热。

如果空间足够大,可以考虑在外围增加散热片,将热量通过该散热片散发出去。

可见有很多能提高该芯片散热的措施。

我们一直使用多年的该芯片布局,用起来一直正常,没有出现过散热问题。该布局参见上图。

有底盘,过孔,大的铜箔,这几个措施就保证了良好的散热。

二.该芯片在使用过程中遇到的另一个问题是:关于前馈电容参数的考虑

不知道大家有没有遇到过前馈电容的一些问题,可以在此讨论一下。

也希望能够获取更多的关于此Cff电容的设计经验.

该前馈电容的作用:

主要是改善瞬态响应,改善转换器带宽,同时仍保持足够的相位裕量。如果优化的很好,可以获取更大的带宽或更大的相位裕量以满足其特定的性能需求。

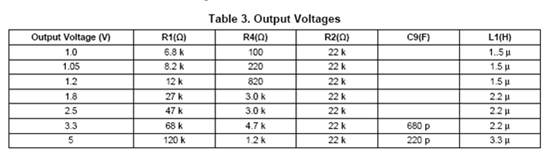

问题引出:最近周围同事在调试他的小板时,发现了一个问题,就是该电容09年给的参考取值是680P,现在的参考变为10-22P。

因为他小板该芯片电路输出纹波过大,有2V多,所以开始怀疑到这个电容,再加上发现了此不一致问题,更有理由怀疑此电容。

考虑到该芯片电路已经应用到几种板上多年,而且量较大,如果真是有问题的话,将涉及到成熟图纸的修改,甚至更换成新电容后的整机装置是否还能可靠运行。

于是这个质量问题交给我来负责查找。

1.首先我看了下他测试纹波的方法,发现他是在电容上焊接两长引线,然后用示波器探头夹住在长引线上测量。

我首先建议他在电容上直接焊接两个电阻腿,将示波器探头触碰到改引脚,充分接触。

这样测量的纹波立刻就降低很多。由上次测量的2V,降低到了几十mV.

2.对于两次给出的电容值差别这么大,很好奇。于是向TI的FAE咨询。

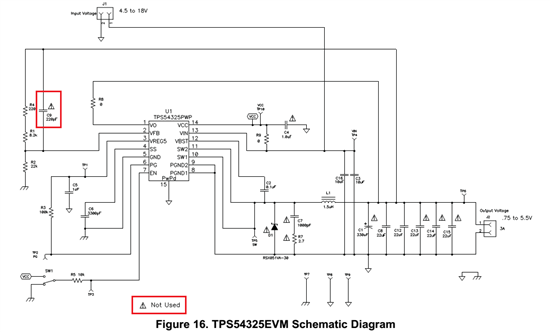

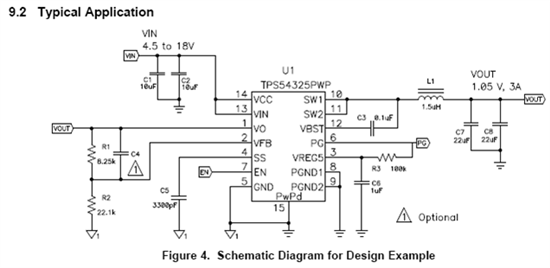

上图是关于该芯片的经典电路,重点是关注那个电容C9。

该电容09年给的参考取值是680P,参考当时的评估板见下图:

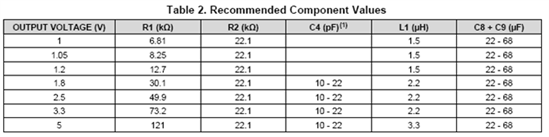

现在的参考是10-22p,

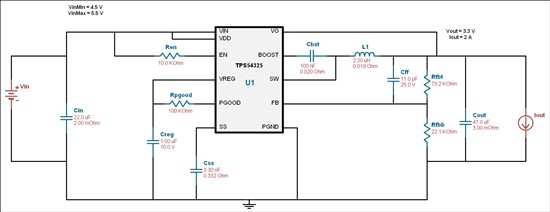

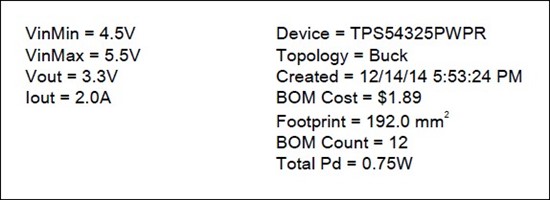

新设计可以利用仿真来获得理想的参数。见下图:

部分仿真设计讯息见上图。

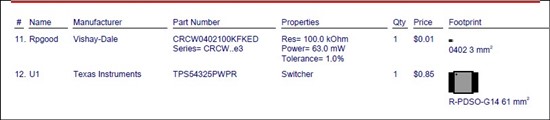

仿真设计的BOM表见上图

3.该同事还反应说,他新做的板子,遇到的问题在将电容改小后就正常了。

所以关于该芯片具体的应用问题,还需要持续关注,也许会遇到因为负载瞬态响应过慢而需要做出相应更改的场合。

关于前馈电容,以后还将经常打交道。不仅仅在这个芯片,同类的芯片也是如此。