12.6v转5v

如题,我的输入是12.6V想要产生5V,输出电流至少1A,之前我用的是LDO,但是发热量太大导致供电不正常。求大神推荐12.6v转5v,输出电流至少1A的DC-DC

HI

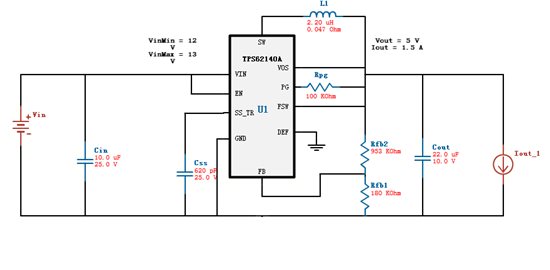

推荐同步降压芯片TPS62140A: http://www.ti.com.cn/product/cn/TPS62140A

简单易用:

Hi

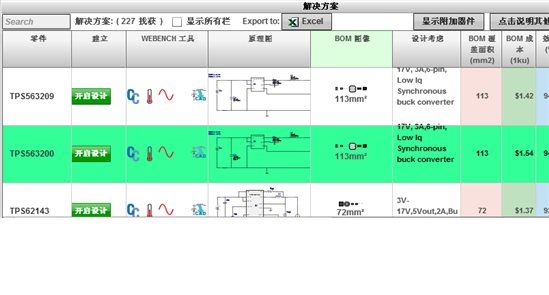

用固定5V输出版本TPS62143更好。

或者用webench 选型,符合的芯片非常多:

在压降这么大的情况下,输出电流也能达到1.5A?我的电路时模拟电路,这样产生的电压是不是还要经过LDO才能不对电路产生影响

HI

不需要,DC/DC转换就是做电压转换的,原理是用开关控制磁性元器件电感来达到降压目的,效率非常高(超过90%,芯片承担的功耗比较小),因此功耗低,发热量小。

LDO是可以做电压转换,原理类似用通过电阻来降压,压差相当于电阻电压,压差大电流也比较大时,功耗就非常大,所以发热严重。(效率40%,芯片承担全部功耗)

我以前就是直接将DC-DC产生的电压接到电路上,没有经过LDO,但是对模拟电路的干扰比较大?现在这样直接产生5V我估计也会带来干扰

你好,如果要避免发热 提高效率,建议贵司还是按照johnsin所描述的选择同步的buck 型dc-dc转换器。诚然在开关模式的dc-dc输出电压会叠加一个开关频率的纹波,但关于你提到的对模拟负载产生干扰的问题需要具体去分析,如果你是指纹波的幅值太大可以通过外围器件的选择,如在不影响环路的情况下增加输出电容容值,用几个小电容并联得到需要大电容的同时降低ESR等等来实现。

如果是这个频率的噪音耦合到后端负载被信号放大的电路中,建议可以通过电源端的退耦以及选择错开后端信号放大频率的开关频率,如果是通过EMI影响到后端的模拟负载,那么可以采取一些降低EMI的措施,如降低开关速度,优化layout减少发射环路面积等等来优化。

当然,如果是非EMi引起的,而贵司的项目可以在牺牲一些成本的前提下,也可以采用dc-dc +LDO的方案,即通过dc-dc得到一个高于预期电压(需要大于后面选择的LDO的vdropout+vout),然后再采用一个具有良好的PSRR性能的LDO得到干净的供电电压,这个方案兼顾了效率和“干净”的供电电压要求,但牺牲了一些成本和pcb layout面积。以上谢谢!