关于TPS40210 5V升9V带大负载掉电压的问题

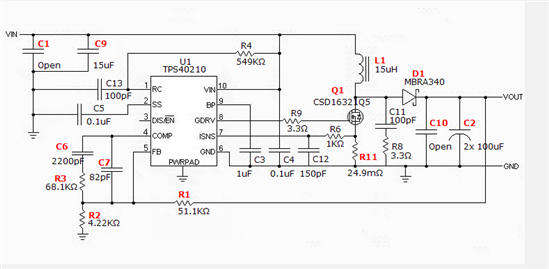

用TPS40210做了一个5V升9V的升压电路,空载可以正常升压,带负载最多只能到9ohm,电压为8.7V左右,再减小的话电压几句下降到7.2V,不知道是什么原因,下面上原理图和波形图,将原理图中的25mohm电阻去掉了

用的是自己焊的面包板,不知道影响大不

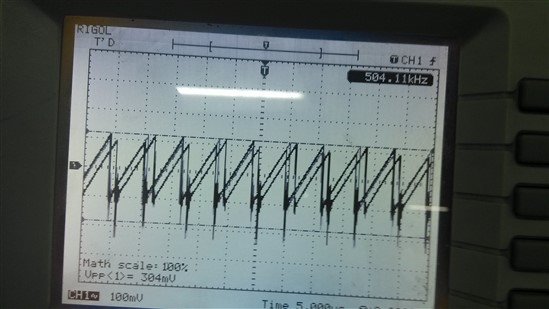

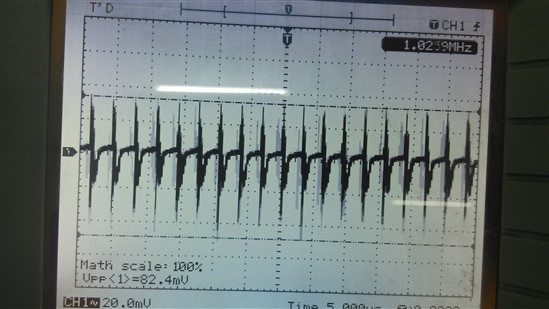

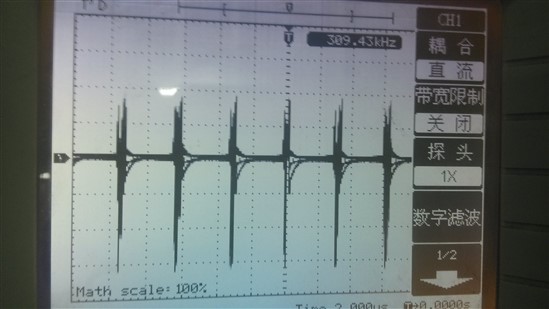

1脚带15ohm与带9ohm的波形

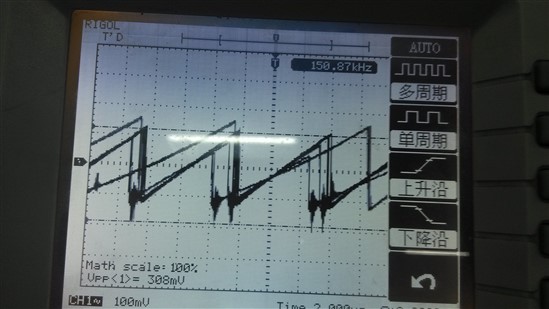

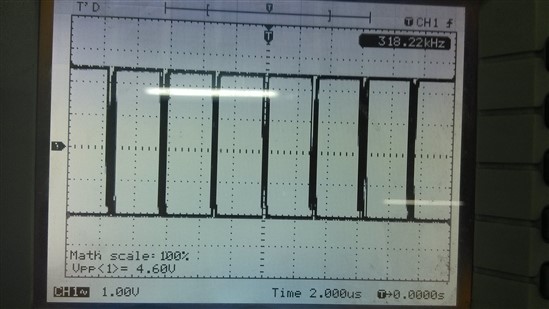

5脚轻载与重载波形

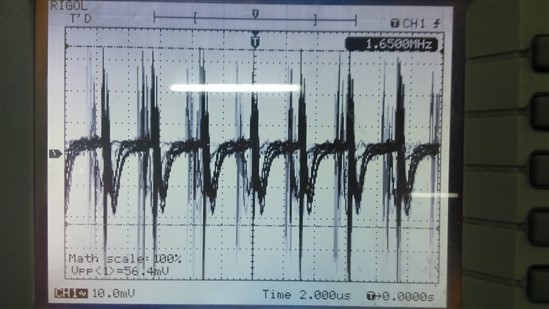

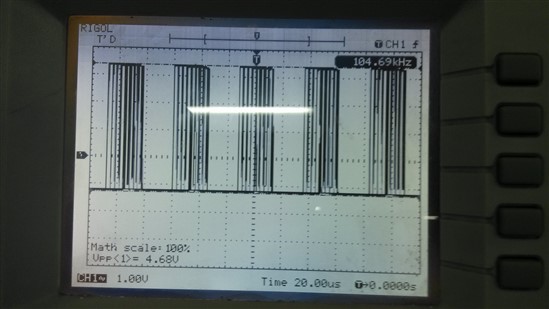

8脚轻载与重载波形

请大牛们帮忙看看,感激不尽

你好,你这波形也太跳了,减小电流采样电阻试试先,如果不是这个问题,检查闭环回路看看,谢谢。

楼主,你设定的输出电流额定值是多少。这里的这个25mohm的电阻不能去,这个电阻是电流采样电阻,必须要接,如果不接,那么电流采样的值一直为零,控制环路会有问题。你把波形再测试一下,触发调好,单次触发一下,看看波形是什么样的。

1:最后一个图是环路震荡了。需要调整环路补偿参数。调节价R3、C6、C7(最好是加大C7)。

2:你测量的第二个图没有用,你需要测量一下7脚的波形,这个能看出很多问题,这个非常重要!

3:看你的8脚驱动波形占空比都快满了,建议在满载时候,测量输入电压有没有跌落过低。

总之,你一定要测量7脚的波形,才能看出更多的问题。

是不是TPS40210的背面散热区没有接地啊?电感值会影响负载,把电感值减小试一下。。

1.测量MOS源级的波形,这个波形可以反映电感是否合适。

2.测量开关节点的波形,这个波形可以反映是否稳定。

3.输入功率是否受限?

谢谢

对的,我的芯片背面没有接,请问这样有影响么?

我设定的输出额定电流是2.1A,加上采样电阻的话带负载能力特别差,就把它去掉了

在工作时候你摸摸芯片有没有发烫。背面如果不连接的话,散热会很差。IC主要就是靠背后的PAD来进行散热的。尤其是大负载的时候。

我试了一下,并了一个100pF的电容,但是貌似没有作用啊

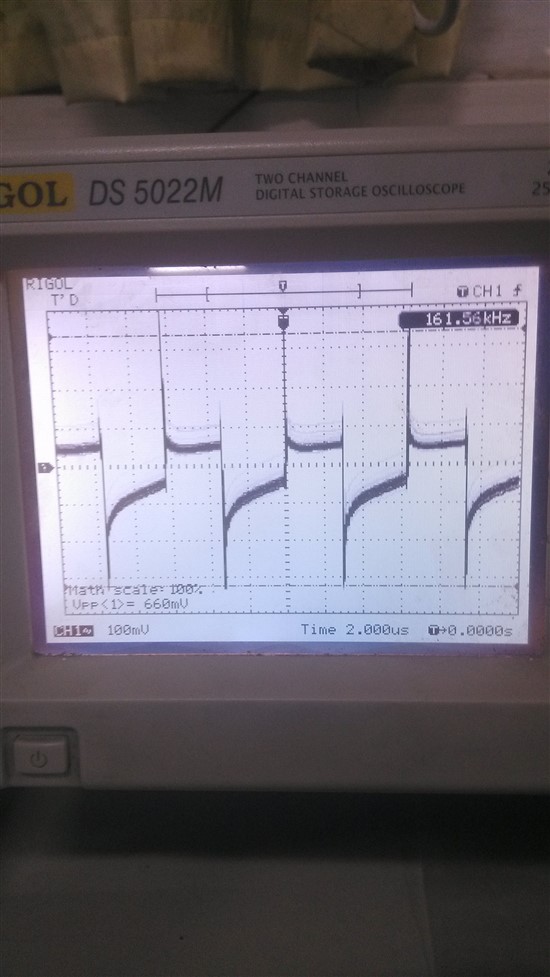

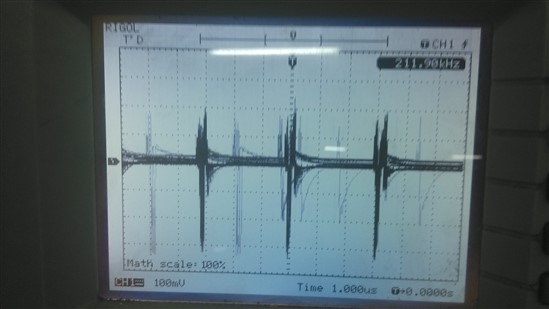

这个是带10ohm负载时7脚的波形,还有那个环路振荡是怎么发生的啊,请您给解释一下

芯片基本上没有热的感觉,这对带负载会有影响么

负载电阻变小的时候会有一个极限值,掉到8ohm以下的时候电感会一直响,然后电压就从8.8V左右掉到6.8V,请问这是什么原因造成的?

你这个波形是第7脚的波形是吧,你的测量有两处不妥。

1:目测你好像调到了交流耦合或者垂直位移不再零刻度。你要确保耦合方式为直流耦合,而且垂直位移应该为0(就是示波器探头接地,那一条水平线应该在零刻度)。

2:你的极性好像接反了。示波器的接地夹接在GND,示波器的探针接在7脚。

建议你观察是否有上述两个错误,如果有的话,请更改之后,再次测量发图。

如果这个波形就是你的7脚波形的话,而且有上面的两个错误的话,那么毫无疑问电感饱和了。

环路震荡的问题是由于R3、C6、C7这几个RC元件的取值,导致PWM的占空比忽大忽小。导致输出有低频的震荡。一般来说,C7越大,稳定性越好,但是环路反应越慢,C7越小,环路反应越快,但是越容易引起震荡。

线没接反,但是确实调的是交流耦合,改过来了

10ohm的负载

5ohm负载图:

R11是电流反馈的测量电阻,不能去。还有您的波形怎么抖动这么严重?

这两个图怎么跟你10:04发的图不一样呢?和你10点04分发的那个图不应该差别这么大啊。

还有,这个电流采样电阻的波形跟GDRV波形好像不太一致呢?

你的这个波形后面有重影是吧,这个重影就反映了电路的震荡。

您好!请问正常的7脚输出应该是怎么样的呢?我也在用这款芯片,输出电流的值一直上不去,想求教一下,谢谢了