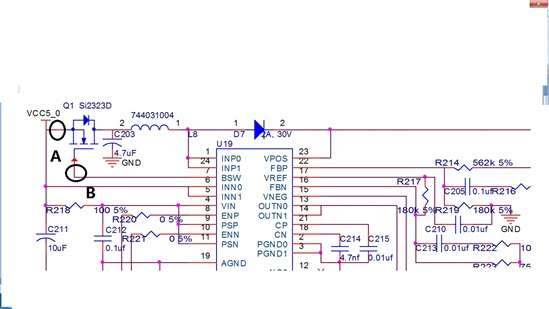

TPS65130关断问题

时间:10-02

整理:3721RD

点击:

输入5V,输出正负5V作为LCD屏的电压,发现在ENP脚拉高后,BSW立马拉低,输出立马会有正5V,但是在ENP脚拉低后,BSW立马拉高到5V,理论上来说pmos管si2323d是关断状态,si2323d的D输出应该是0,但是我们用示波器测试发现mos管的D端的输出是一个缓慢下降的过程,从5V下降到0V基本上需要20秒到30秒左右时间!似乎没有立马关断!我们采用物理开关替代si2323d,关断后,开关输出端,也就是原先si2323d会立马变0(虽然有个坡,但是很快,差不多几个ms),之后会有一个0.5v的上升,然后再慢慢回落到0v,这个缓慢下落跟5V下降到0V时间差不多,请问是什么原因导致si2323d没有关断效果?能否帮忙分析一下?

你好

1.建议楼主在AB 加个上拉电阻试试.