关于LM5069短路保护restart过程的问题

使用LM5069-1做验证实验,这款芯片可通过Timer脚的充放电实现一个在过流或短路时的手动restart过程。

在验证短路保护时,发现在短路时由于电流瞬间增大,芯片立即拉低驱动输出,关断MOS管,这个是与芯片资料一致的,随后芯片进入了restart过程,经过一段时间Timer引脚充电到4V时,芯片又开通了MOS管,当然此时依然处于短路状态,但问题是,,此时开通后电流并未瞬间增大,而是被限流了,随后进入了限流重启的过程,随后就一直循环限流重启,这个与芯片资料仿佛找不到合理的解释。

以上实验条件:Vin=28V,采样电阻=10毫欧

而当实验条件:Vin=28V,采样电阻=20毫欧时,短路实验前面过程都一样,但是就不会循环重启。

请问有没有人知道这是怎么回事?

PS:芯片为LM5069-1没有错,已确认。

可否将你的原理图贴出来,各阻值都标明

仔细读了datasheet,请你测试一下短路时LM5069-1的输入电压,有没有低于UVLO的点。

这就是弥勒效应与保护延迟共同作用后的结果。与IC机制不完全相关。

有可能电源到LM5069的引线太长太细

10毫欧,限流为5.5A

20毫欧,限流为2.75A

5.5A引起的线损更大,所以到芯片端的电压降低很多,可能低于你设定的UVLO点

我们也怀疑是短路时VIN端的电压突然降低又升高引起芯片重新上电的过程,当时可能测的是输入电压的源端,所以没有看到电压降低的现象,我们会再验证一下。

谢谢你!

不客气

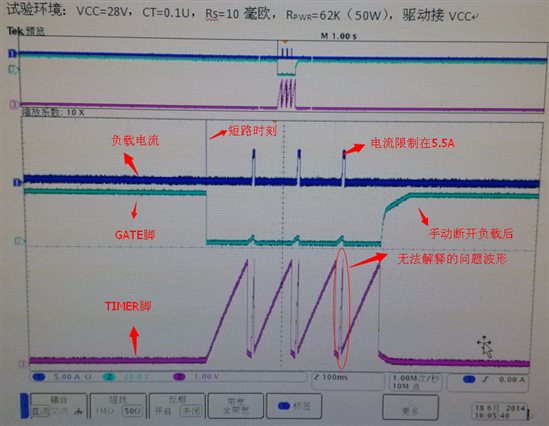

测了短路时VIN端和UVLO端的电压,并没有下降很多,VIN和UVLO都是28V,短路时VIN和UVLO电压下降约1.6V,且MOS管在重启时处于半开通状态,GATE脚为4V,管压降约2.4v,下面附上测试图片:

其中,OVLO接地,用UVLO接VIN端开通MOS管,UVLO接地时关断MOS管,PWR端悬空,TIMER接0.1uF电容。

画圈的地方就是帖子开始说的,过载保护后放电电流为1.5A且放电后有进入重启过程,请问这个现象如何解释?

按照回复说的导线在短路时损耗并未大到使VIN端电压下降很多。

你为什么要把PWR悬空呢?datasheet中没有说可以悬空啊

你说Gate有4V电压,我估计是进入power limit功能了。

接仔细看datasheet中关于power limit 的描述

datasheet中Power Limit里说如果不用功率限制可以将PWR管脚悬空。

而且当GATE有4V电压时,OUT端电压并没有上升到和VIN一样 ,而是一个很小的值,说明MOS管并未完全开通。

此外,请问芯片是靠什么去判断用哪个电流源进行放电的?短路后重启时的电流限制,timer脚以85uA电流充电,然后却以1.5mA电流放电,请问这里为什么不是用2.5uA放电呢?