tps53355,带3A以上负载LL脚震荡

原理图按照datasheet上的建议电路所搭。5V转3.6V。

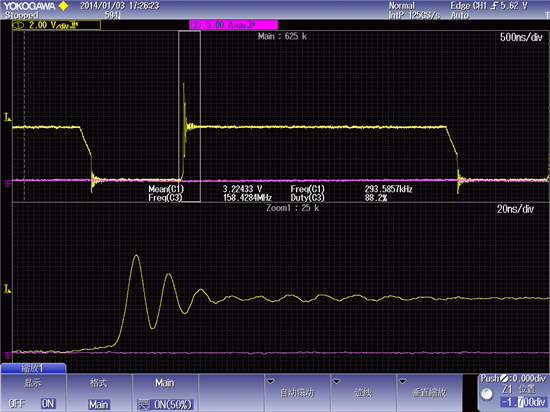

上图是输出0到2A时的LL脚上的波形。

上图是输出3A时LL脚的波形。

上图是输出从3A变成3.1A时LL脚波形。不知道为什么3A时波形只震荡2,3次,3.1A时震荡突然多了这么多。并且导致效率突然下降,输出电压下降。

上图是我进一步加大负载至4A,黄色为LL波形,红色为输出电感上波形。

1. 有没有检测带载后输入电压的值?要确保Vin不能欠压。

2. 请问VBST与LL之间的电容多大?

你接的是哪种模式,电感纹波耦合的还是输出电压纹波采样的

请发原理图出来看看

Vin电压一直大于1.5V。

VBST与LL之间是1Ω和104的电容串联。

现在改变LL与地之间(这个电路是否为snubber电路?)串联的电阻电容,带载能力得到改善,现在最大能带9A负载。LL与地之间是1Ω与224电容串联。

现在的问题是负载大于5A后效率上不去。而且输出负载调整率也差不多有4%了。

| 输出电流 | 输出电压 | 输入功率 | 效率 |

| 1A | 3.69V | 4W | 92.3 |

| 2A | 3.67V | 7.92W | 92.7 |

| 3A | 3.66V | 11.06W | 91.8 |

| 4A | 3.64V | 16W | 91 |

| 5A | 3.62V | 20.36W | 88.9 |

| 6A | 3.6V | 24.8W | 87.1 |

| 7A | 3.58V | 29.45W | 85.1 |

| 8.5A | 3.54V | 36.73W | 81.9 |

试过Auto Skip和Force CCM两种模式。

不太明白你说的电感模式指的是什么。由于手头没原理图,今晚临时整了一个。贴上来一起讨论。你看这样是纹波耦合还是纹波采样?

4718.tps53355.rar

现在还出现的一个问题是带载大于4.2A启动不了,减小负载至4.1A时可以正常启动。我贴几个主要管脚的图一起讨论下。

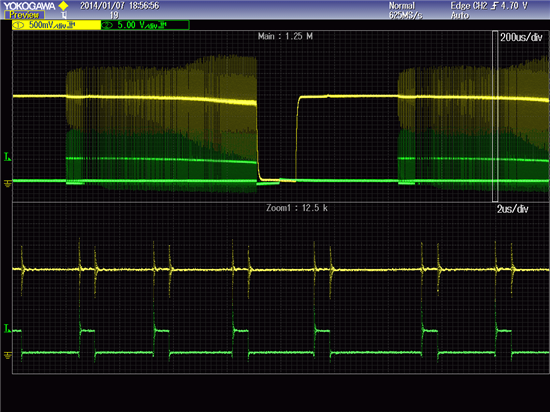

上图黄色为RF脚,绿色为LL脚。下半屏为上半屏白色竖条的放大。

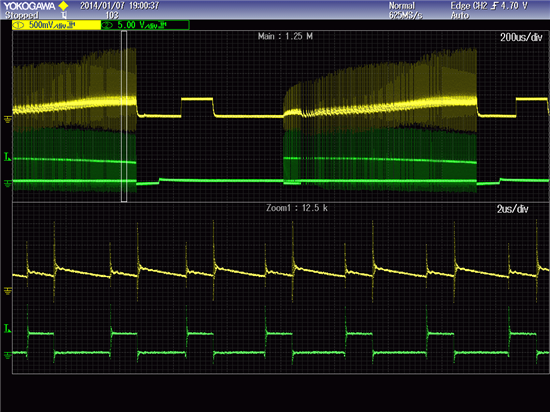

上图黄色为TRIP脚,绿色为LL脚。

上图黄色为MODE脚,绿色为LL脚。

上图 黄色为VDD,绿色为LL脚。

上图黄色为VREG,绿色为LL脚。

上图为黄色为VIN,绿色为LL脚。

上图为黄色为PGOOD,绿色为LL脚。

上图 黄色为VBST,绿色为LL脚。