PTEA415050高温续流管失效请教

我们有使用贵公司的一款DCDC模块PTEA415050,这个模块在我们产品老化的时候失效,失效率较高,3%,表现为5V无输出,输出管脚短路,进一步定位发现续流管异常,此DCDC模块的同步整流驱动为TPS2834,测试驱动波形为

其中黄色为续流管驱动波形,蓝色为开关管驱动波形。

目前的问题是:

1、此驱动波形有没有问题,在续流管关断时有死区时间,在开关管关断没有死区时间?

2、此款DCDC模块有没有做过设计更改,发现最近的失效的这一批的开关管及续流管的丝印跟之前的不一样,能否提供这两个管子的型号,管子的开启电压?

3、续流管失效的原因有哪些,我们用的贵公司的TPS54320也有发现也是续流管坏的,我们可以从那几方面去排查?

以上,希望得到各位专家的回答,谢谢!

canjun deng

我们有使用贵公司的一款DCDC模块PTEA415050,这个模块在我们产品老化的时候失效,失效率较高,3%,表现为5V无输出,输出管脚短路,进一步定位发现续流管异常,此DCDC模块的同步整流驱动为TPS2834,测试驱动波形为

其中黄色为续流管驱动波形,蓝色为开关管驱动波形。

目前的问题是:

1、此驱动波形有没有问题,在续流管关断时有死区时间,在开关管关断没有死区时间?

2、此款DCDC模块有没有做过设计更改,发现最近的失效的这一批的开关管及续流管的丝印跟之前的不一样,能否提供这两个管子的型号,管子的开启电压?

3、续流管失效的原因有哪些,我们用的贵公司的TPS54320也有发现也是续流管坏的,我们可以从那几方面去排查?

以上,希望得到各位专家的回答,谢谢!

回答第一个问题:看驱动波形,在开关管关断时,死区时间不明显,建议看一下BOOTLO的波形,是否有死区。

2、此款DCDC模块有没有做过设计更改,发现最近的失效的这一批的开关管及续流管的丝印跟之前的不一样,能否提供这两个管子的型号,管子的开启电压?

回复:丝印上面不但包含了芯片的Part number,还有晶圆生产日期,批号,不一样是正常的,每个芯片在出厂之前都经过测试,肯定满足datasheet的EC table的要求,能否提供你所说的丝印的区别

3、续流管失效的原因有哪些,我们用的贵公司的TPS54320也有发现也是续流管坏的,我们可以从那几方面去排查?

回复:如果没有死区时间,续流管和开关管都有可能坏掉。

如果要降低可能性,可以考虑在boot电容上面串接电阻,降低开关管开通速率,或者加snubber,减慢驱动。详细请参考文献:

Ringing Reduction Techniques for NexFETTM High Performance MOSFETs

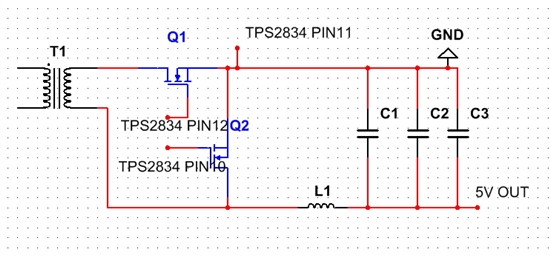

多谢Osial的回复,看了一下DCDC模块的大概电路结构,如下图

TPS2834 BOOTLO是接地的,测试不到波形。上面的示波器图就是开关管及续流管的驱动波形。上面与测试波形TPS2834datasheet上 dead-time (DT) control中The high-side driver is not allowed to turn on until the gate drive voltage to the low-side FET is low, and the low-side driver is not allowed to turn on until

the voltage at the junction of the power FETs (Vdrain) is low明显不符。

丝印区别见下图:

从芯片表面上看,应该不是Part number,晶圆生产日期,批号不一样,应该是两个不同型号的芯片。能否提供这两个器件的datasheet资料。

ptea415050是购买的贵公司的电源模块,boot电容上串电阻比较难实现。

TPS54320是内部集成了FET的,无法测试FET的驱动波形,TPS54320的datasheet上有写 A boot resistor in series with the boot capacitor should never be used on the TPS54320。不知道串电阻对其带来其他的影响。

canjun deng

多谢Osial的回复,看了一下DCDC模块的大概电路结构,如下图

TPS2834 BOOTLO是接地的,测试不到波形。上面的示波器图就是开关管及续流管的驱动波形。上面与测试波形TPS2834datasheet上 dead-time (DT) control中The high-side driver is not allowed to turn on until the gate drive voltage to the low-side FET is low, and the low-side driver is not allowed to turn on until

the voltage at the junction of the power FETs (Vdrain) is low明显不符。

如果你提供的电路原理图是正确的话,DT直接连到GND。

从TPS2834的框图来看,由于检测到的DT一直为低(因为连着地),那么一旦开关管的栅极电压下降,续流管就会导通,上下管溃通的几率还是很大的。

从波形上看,也符合前面的推测。

从丝印上看,不太像TI的FET,要不你去TI全球客户支持上发帖问问。网址是e2e.ti.com, 可能需要注册及使用英文发帖。

canjun deng

ptea415050是购买的贵公司的电源模块,boot电容上串电阻比较难实现。

TPS54320是内部集成了FET的,无法测试FET的驱动波形,TPS54320的datasheet上有写 A boot resistor in series with the boot capacitor should never be used on the TPS54320。不知道串电阻对其带来其他的影响。

这个问题我也回答不上来,我在e2e上发帖帮你问了

Osial

canjun deng

ptea415050是购买的贵公司的电源模块,boot电容上串电阻比较难实现。

TPS54320是内部集成了FET的,无法测试FET的驱动波形,TPS54320的datasheet上有写 A boot resistor in series with the boot capacitor should never be used on the TPS54320。不知道串电阻对其带来其他的影响。

这个问题我也回答不上来,我在e2e上发帖帮你问了

他们的回复是:I am not sure of the details, but some devices are not suitable for BOOT resistor use. It has been several years since we looked into this. If you need to reduce overshoot and ringing you will need to use an RC snubber forTPS54320.

仅供参考。