TPS54418 Power good频繁输出低电平

你好,具体问题和现象描述我都在附件里描述清楚了,如果还有不清楚的地方,请告知,非常感谢。

3V的输出有没有问题?PGD信号也是通过5V输入上拉的?

Hi

问题出在输出电压,能否提供输出电压的波形(比较清楚一点的)

3.0输出正常,但是文波要比常温下大了300mV左右,我不知道是否受干扰所致还是电路本身的影响,PGD信号时上拉到5V上的。

Hi

Vsense偏离规格Vref的91%和107%,会导致powergood输出变低。

输出3V或者还在规格内,但是如果纹波或者noise过大,可能导致Powergood误动作。

检查一下你的输出电容(以及环路补偿的电容), 看看在低温操作下的特性,如果容值偏离比较大等等,这个都可能导致电源的稳定性下降的。(电容建议选择温度系数较好的材质,如NPO, X7R等等。

TPS54418的纹波实际是非常小的,按照datasheet上1.8V的案例,是小于30mV的。按照你的设计,3V输出,纹波大于300mV, 最低电压已经偏离规格10%了,这个是可能导致Powergood误动作的。

常温下纹波多大?把对比波形贴上来看看。输出电容用的什么型号?

Hi

或者你可以直接加大输出电容再测试(可以再并联)看看?

您好,附件是纹波比较大的和纹波比较小的两个图,都为绿色,纹波较大的是在低温下测的,纹波比较小的是在常温下测试的。

电容的大小我们试过22uF,33uF,47uF,55uF,69uF,80uF,147uF都没有效果。

电容的型号我还需要和我们的采购联系一下确认。

您好,我们采购说我们的钽电容采购的是AVX的,是X7R的,陶瓷电容采购的是三星的,部分是村田的,有的是X7R的,有的是X5R的,不过上面的焊的是否X5R的就不知道了,X5R的也是能过-40的,所以我觉得应该不会有问题。

Hi

在输出并联一个陶瓷电容看看, 原因是钽电容的ESR是比较高的, 按照datasheet推荐输出一般采用低ESR的陶瓷电容,例如两个22uF并联。

如果你用钽电容,建议采用低ESR的钽电容,并且采用多个并联以达到降低ESR的目的.

您好,按您的建议更换了陶瓷电容,但是效果还是和采用钽电容的一样,随着温度变低,纹波逐渐增大。

您好,有没有方法可以调整这个精度范围,或是如何减少Vsence这个管脚的敏感度?

目前还有一个现象,就是输入电压越高,纹波越大。

Hi

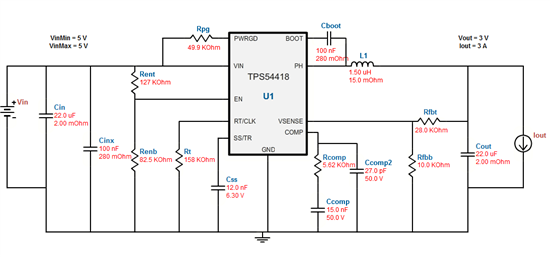

见如下是TI wenench仿真的电路设计:

你或可以参考,因为你的电路设计,可能纹波比较大,建议做如上修改。如果测试仍然有问题 请将SW的波形传给我(常温下和低温下的),我需要看的参数是频率,占空比。(注意上图器件的参数)

在你的设计中要注意,输入电容(10uF+4.7uF)尽量要靠近芯片脚。

Hi

请问是否确认到问题所在? 请回复。

您好,还没有确认,无法解决问题,我上传了纹波的放大的图,您帮我确认一下这类型的纹波是什么类型的纹波,一般这类纹波是什么导致的,如何解决。

您好,你们有解决办法吗?

Hi

纹波达到了800mV左右吗?

有没有按照我之前提供给的webench仿真的电路的零件规格修改,然后测试?

您好,我们测试纹波的方法存在问题,实际的纹波也就是46mV~50mV之间,没有那么大,器件的选型时按照Webench提供的要求采购的。