TPS5430 ENA管脚容易受干扰,请教如何处理

ENA 没有外接控制,在用手触碰,或者ESD 4KV的时候,TPS5430 容易不输出,导致整个系统复位。请教怎么解决这个问题,或者有其它替代芯片?

ENA是悬空的吗?考虑上拉,再挂一个Y电容。

另外,pin2pin替代的话,考虑一下TPS5431,不过输入范围才到23V,非pin2pin的话降压方案很多,到TI官网选一下

http://www.ti.com.cn/lsds/ti_zh/analog/powermanagement/power_portal.page

输入电压是多少伏?建议通过上拉到输入电压,通过分压高于0.5V便可使能芯片。

上拉到电源输入不行,上拉100K左右的时候,5V输出会变成5.8V左右, 上拉电阻太大,对抗静电不起什么效果

输入24V, 实际输入高压可能达到30多V, 低压大概10V(因为输入电容的能量需要在掉电保存方面继续使用), 所以不能通过电阻(或者稳压管)分压解决

可以试试TPS54362-Q1。EN和VIN一样耐压60V。

http://www.ti.com.cn/product/cn/tps54362-q1

楼主,挂电容有试过吗?

Kevin Chen1

,挂电

上拉电容到VIN,和下拉电容到GND 都试过,没有作用

设计的系统是否带外壳?

Hi,

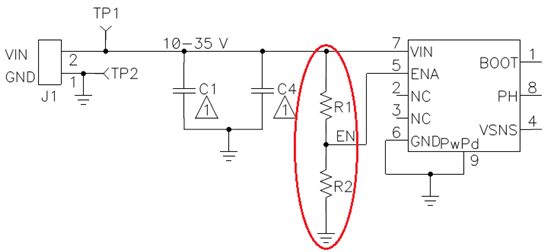

你将EN引脚外接电阻分压网络,固定在一个电压试试(如3V),如下图所示。EN引脚开启阈值电压为1.3V,你的VIN最高为30V选取R1=100k,R2=11k,使VIN在30V时EN引脚电压为3V,当VIN为24V时,EN电压为2.4V,仍能保证芯片使能。注意EN引脚可以承受的绝对最大值电压为7V。

EN引脚悬空时,会由内部5uA上拉电流源上拉至约5V,这个电流源上拉比较弱,用手触碰引脚时,手与ground以及大地之间的回路有可能将EN引脚拉低从而使芯片disable掉。

Thanks.