请教——关于LM25011第3脚PGD的问题

时间:10-02

整理:3721RD

点击:

本人菜鸟,有个问题真诚请教。

本人菜鸟,有个问题真诚请教。

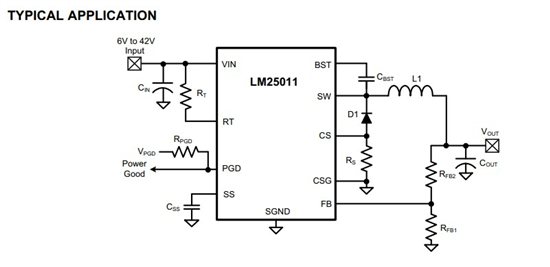

我有个设计想使用LM25011做24V输入,5V(1.8A)输出。但我查看LM25011资料后,对他的第3脚PGD不太理解。典型应用图如上图。

问题如下:1、如何应用这个引脚?

2、悬空此引脚可不可以?

3、如果接10K上拉电阻的话,是不是可以通过输入24V分压出5V来做VPGD?

Hi

PGD是输出正常指示脚,当输出电压正常,而就是FB分压达到内部基准电压95%时PGD即可输出高电平,但是PGD是Open drain的MOS结构,所以需要上来一个小于7V的上拉电压。当输出正常(超过95% 内部基准)MOS关闭,PGD输出即上拉电压(扣掉Rpgd的压降)。

如果不需要输出正常指示这个功能,你可以悬空PGD。

可以上拉一个电压,如输出,但是不建议用24V分压,原因是假设24V分压是6V,那么6V分压就是1.5V,这个要看你后面接的受电设备的需求,一般选个稳定电压比较好。

现在明白了,非常感谢您的解答。

主要是用于使能其他电路,在ATX电源中应用比较多。