9244输出为0

如题,用fusion软件配置9244+7242给DSP供电,将工程写进9244的flash里面为什么输出一直是0?请教TI专家以及论坛的大侠们这有可能是什么问题?如果有成功调出的朋友们可否分享一下你们的工程或者给一些建议也行,万分感激了,拜托。。。。期待专家的回复

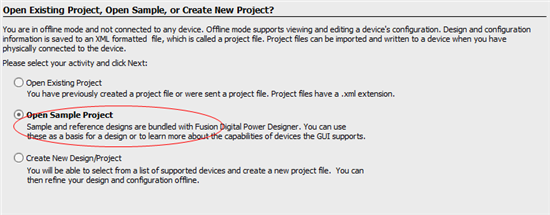

可参考软件中自带的UCD9240的工程,或者参考下面附件自己建议工程。

http://www.ti.com.cn/analog/cn/docs/litabsmultiplefilelist.tsp?literatureNumber=sluu490&docCategoryId=6&familyId=688

首先感谢Trevor的建议,我将按照你的建议试一下

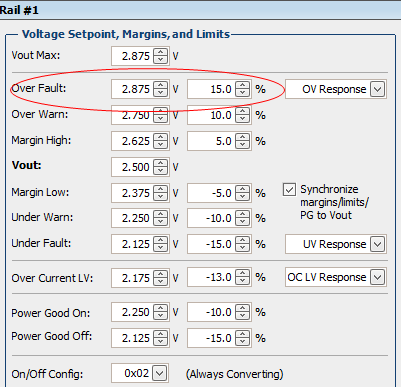

再次请教Trevor,为什么老出现FLT错误?这个错误可能由什么引起?

具体是OT FLT,还是OV FTL或是其他FLT?应该是参数设置问题。

是 OV FLT,还有我参数设置里面VID都是选的ignore VID input选项,另外我知道vin scale,vout scale loop,vout monitor和Iout cal gain,Iout cal offset等参数是起校准作用的,我配置的时候这些参数大多选的软件自动计算出来的值,还有compensation MODE 也选的AUTO tune,频率300K-1000都试过,其他参数应该没什么问题了。可是配置起后不能产生输出呢?不知是否还有需要特别注意的地方?先谢谢Trevor工程师的耐心指导,由于都是第一次用这种片子,所以经验不足。

输出电压设为多少?高出多少%后报错?

试着加大报错的%看可不可?

这个问题解决了,还有几个问题,就是用GUI Design里面的edit full power stage in schematic 设计出的电路图里面的器件值如果与我自己电路图里器件值不一样的话,是否需要加以修改才行?

具体是哪个值不一样?能否贴个图?有些器件伯值不一样,只是影响环路响应的增益跟相位的裕量。

一般是需要软件上配的跟你外围电路是一样的。

Rcs与Ccs。

就是CS引脚Imon引脚之间的Rcs和Ccs,网速问题传不上来图,不好意思了

软件上是根据软件中的参数进行仿真,给出波特图,供参考。如果与实际板子上一致的话,可以做为实际板子上的环路分析。但这只是个参考,建议还是用专门的环路分析仪来测试下实际板子的环路设计是否稳定。

谢谢Trevor的回答,但是我不太明白怎么测试环路设计是否稳定。我发现一个问题,就是我的9244的PWM输出电压是1.65v,就是说会shut off7242的high side MOSFET和low side MOSFET,就不会有输出,不知道是什么原因引起的?后来我自己产生了一个占空比10%的1M的PWM波直接输入7242的PWM引脚,结果还是不能有输出。