UCC28950倍流同步整流

您好!本人用UCC28950设计一款DC/DC,指标如下:

输入电压范围:320V(280V-360V)

输出:12V,100A

拓扑结构:前级移相全桥,后级倍流同步整流。驱动电路与TI开发板一样。

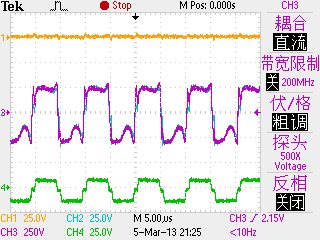

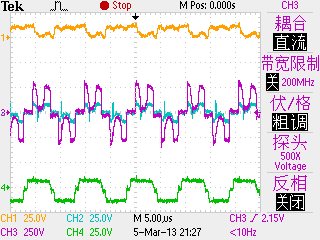

主电路图详见附件。插入的两张波形图分别为20%负载和30%负载时的波形图(CH1为同步整流管GS,CH2为主变二次侧电压,CH3为主变一次侧电压,CH4为全桥其中的一个管子的GS)。

调试遇到问题:

1、用恒流电子负载进行调试,由波形图可以看出负载没有超过20%还算正常,但所加负载到30%后变压器开始打嗝响,变压器两侧的波形完全变形了,没有输出。

2、随着负载的增加,输出电压越来越低,到接近30%负载时没有输出。

3、请问要在什么情况下UCC28950的OUTE和OUTF才有输出?怎么一直没有见到过?

建议:

1:测一下在30%负载情况下,四组驱动信号的逻辑是否正常?

2:UCC28950的12引脚DCM是来设置同步整流信号的门槛值的,当CS脚的电压在DCM引脚电压值以下时OUTE和OUTF无输出驱动。检查DCM引脚的门槛值和测量CS脚的电压。

1、30%负载情况下四组驱动信号与低于30%负载情况下没有任何变化。

2、我观察到随着负载的上升输入电压略有下降,是不是我的输入电容小了?

3、随着负载的上升输出电压的下降是不是因我的反馈回路有问题?

4、谢谢您的回复!本人研二,是在没有任何人指导之前也没有任何经验的情况设计的这款DC/DC,现在调试起总感觉无从下手!

David Ji

建议:

1:测一下在30%负载情况下,四组驱动信号的逻辑是否正常?

2:UCC28950的12引脚DCM是来设置同步整流信号的门槛值的,当CS脚的电压在DCM引脚电压值以下时OUTE和OUTF无输出驱动。检查DCM引脚的门槛值和测量CS脚的电压。

1、30%负载情况下四组驱动信号与低于30%负载情况下没有任何变化。

2、我观察到随着负载的上升输入电压略有下降,是不是我的输入电容小了?

3、随着负载的上升输出电压的下降是不是因我的反馈回路有问题?

4、谢谢您的回复!本人研二,是在没有任何人指导之前也没有任何经验的情况设计的这款DC/DC,现在调试起总感觉无从下手!