BQ76930 cell balance问题

时间:10-02

整理:3721RD

点击:

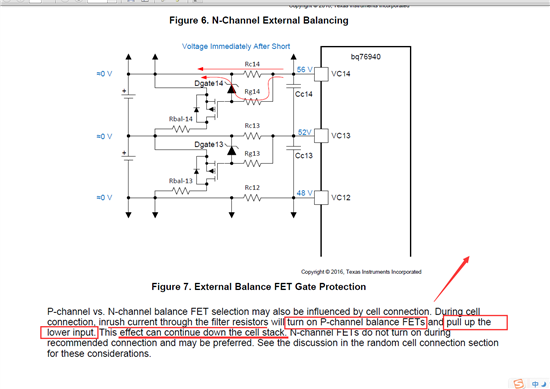

Figure 7. External Balance FET Gate Protection 这点讲到对均很MOS的G极保护问题,我一直看不懂到底是描述的是什么意思。

1,inrush current through the filter resistors will turn on P-channel balance FETs and pull up the

lower input 短路后,浪涌电流会通过滤波电阻打开均衡MOS,并且拉高低平输入。

我是这个理解的,短路后电芯电压接近0V,滤波电容Cc14上面的电荷会流过Rc14,Rg14,但是我根本看不出来 这个过程对均衡MOS的G极有什么影响?G极是需要低电平驱动的。

还有pull up the lower input 拉高低平输入,这个又是什么意思?

2,This effect can continue down the cell stack 此种影响将会持续到级联电芯,这句话又是什么意思?

Cell connection瞬间,Rc14上的电流是从左往右,经过Rc14到Cc14,瞬间inrush current很大,会产生一个压降,这个电压是施加在PFET的SG端。对于P管,VSG电压大于Vth后,FET会导通。这个过程相当于给Cell放电。所以文中这么讲。

谢谢,我理解了。

我有疑问,就算是P管被导通,CELL放电,时间应该是很短,电流也不大吧? 对整个电池组影响不大吧