bq20z95EVM开发板中两个不同地的连接问题

你好,

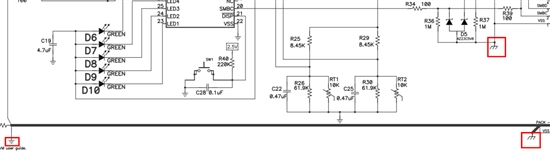

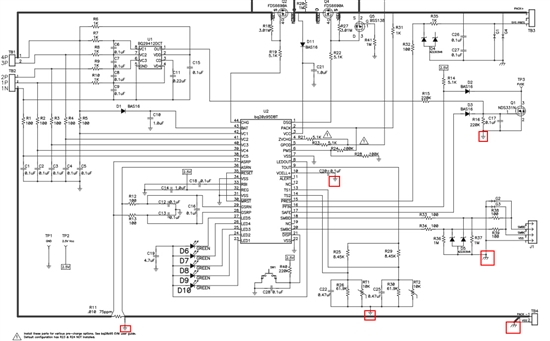

bq20z95EVM开发板中两个不同地的连接问题,是怎么处理的。看图好像两个不同的地直接连在了一起?

既然直接连载了一起为什么还要分开为两个不同的地呢?

这是电路里,为防止互相干扰而采取的措施。

这个是因为对于ESD保护器件来讲,应该尽可能的靠近连接端子,也就是接地应该是P-. 而对于芯片采样控制部分的地,应该在靠近采样电阻的地方采用单点接地。所以虽然是同一个网络,在走线上面是需要区别对待的。

这样做主要是为了抗干扰而设计的。

Hi Richard,

谢谢你百忙之中的回复,对于ESD保护器件我这样处理

1.ESD保护器件靠近Pack-

2.芯片采样部分的地,单点接地

这样理解到位吗?那这两个不同的地最后我怎么连接在一起呢?

还是他们就是同一网络,直接相连只要注意器件的接地方式呢?

PCB布局该注意什么呢?

对,是两个地。一个是模拟地(三na),一个是数字地(三横的)。在一些电路中,有数字电路和模拟电路的,它们的公共地是独立的,但是最后会通过一个 0 欧姆 的电阻串接起来,主要起到隔离互相干扰的目的。

有意思了,有的居然跟不上

这样做就是为了防止干扰信号的, Richard Tang说的很对,要注意布线哦

Hi en,

这个电路中我没有找到0欧姆电阻,是不是可以排除通过0欧姆电阻短接的?

所以看到这个电路比较困惑,不知道PCB怎么处理的。

Hi WEiMIN,

这句话啥意思,没有理解

Hi Zhetao,

你的理解是对的,这个不同地标号的目的就是说明在layout上面的处理的不同。不用担心他们的连接问题,因为板子上面从采样电阻到P-的大电流通路是连通的,就如原理图里面一样,本身是同一个网络。PCB布局的基本原则是大电流回路和小信号回路隔离,大电流回路面积尽可能小。电流采样输入滤波器件尽可能对称摆放,尽可能靠近芯片。走线采用开尔文连接,平行等长等过孔,用信号地进行包围屏蔽更好.

有些电源中的这样的画法表示是通过螺钉连接到外壳,对EMI以及防雷有好的效果

一个是模拟地(三na),一个是数字地(三横的)。在一些电路中,有数字电路和模拟电路的,它们的公共地是独立的,但是最后会通过一个 0 欧姆 的电阻串接起来,主要起到隔离互相干扰的目的。

ESD靠近器件端口

采样部分单点接地,但是接地端的面积一定要大→即实现较低的阻抗,因为采样电流较大,所以即使很小的阻抗也会产生客观的压降,这点要注意。

关于不同的地,是为了数字模拟隔离使用。如果对这块没有要求,直接连在一起即可。如果需要完全隔离,例如使用变压器线圈实现隔离输出,那么两个还是要分开的。

如果为了获得更好的信号完整性能,但是又不用隔离,怎么办?这两个地应当单点连接,即通过0R电阻连接。(一般0R电阻我们即可以认为是单点接地。)

这两个地是连在一起的,但是不能直接相连接。

两者之间需要通过一个0欧姆电阻或者一个磁珠进行隔离,防止干扰。

Hi JiaChuang,

谢谢你的回复,开始我也这么认为。是不是通过了0欧姆电阻或者磁珠进行隔离处理。但是找遍原理图,并没有发现0欧姆电阻或者磁珠。

Hi Zhetao,

你好,请不要受一些回复的影响,这个不同地标号的目的就是说明在layout上面的处理的不同。从电气上面来讲就是一个大电流通路,这个地方在这里也无关信号干扰的问题,就是ESD器件靠近端口以获得最短的ESD回路。不用担心他们的连接问题,因为板子上面从采样电阻到P-的大电流通路是连通的,就如原理图里面一样,本身是同一个网络。

而对于BQ20Z95本身的小信号参考地,跟大电路地之间,在采样电阻处单点接地就好了,这里没有画出来0欧电阻,采用一个小铜皮连接即可。

PCB布局的基本原则是大电流回路和小信号回路隔离,大电流回路面积尽可能小。电流采样输入滤波器件尽可能对称摆放,尽可能靠近芯片。走线采用开尔文连接,平行等长等过孔,用信号地进行包围屏蔽更好.

Hi Richard,

谢谢你的回复。经过一番讨论解决了很多疑惑。再次感谢你。