我是基于vhdl做了一个简单的两位数计算器,为什么老是有问题

时间:10-02

整理:3721RD

点击:

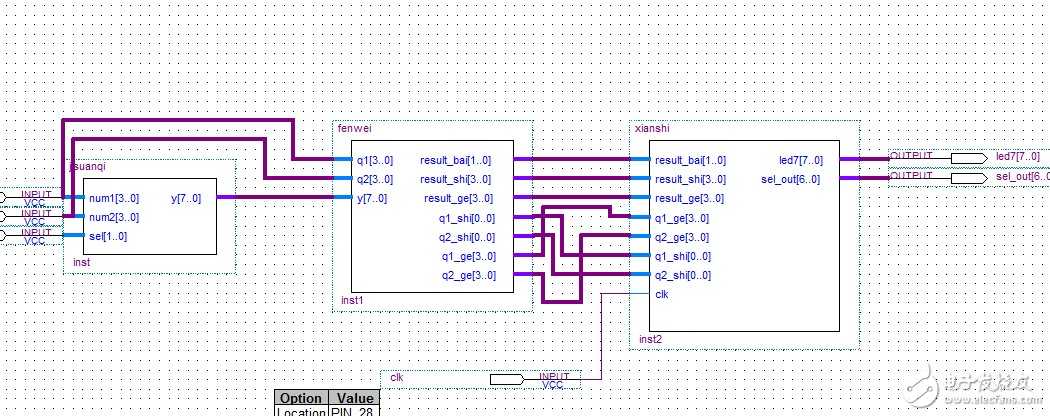

我是用vhdl做的一个简单的两位数的加减乘除运算,输入的两个数只能是0-15,就算的结果是0-225,整个程序是没错的,可是总是在连线后,用数码管分别显示输入的两个数和计算的结果时,输入的两个数的十位总是显示0,其他的显示都是对的,求大神帮我看看,万分感谢!

模块一:计算模块

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity jisuanqi is

Port (num1,num2: in integer range 0 to 15;

sel: in STD_LOGIC_VECTOR (1 downto 0);

y: out integer range 0 to 225);

end jisuanqi;

architecture rtl of jisuanqi is

signal q1 ,q2: integer range 0 to 15;

signal choice: STD_LOGIC_VECTOR (1 downto 0);

signal result: integer range 0 to 225;

begin

choice<=sel;

process(q1,q2,result,choice)

begin

case choice is

when "00" =>

result<=q1+q2;

when "01" =>

if(q1>q2)then

result <= q1-q2;

else

result<=q2-q1;

end if;

when "10"=>

result<=q1*q2;

when "11"=>

result<=0;

end case;

end process;

q1<=num1;

q2<=num2;

y <= result;

end rtl;

模块二:分为模块,将每个数字的位分离出来

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity fenwei is

Port (q1,q2: in integer range 0 to 15;

y :in integer range 0 to 225;

result_bai: out integer range 0 to 2;

result_shi: out integer range 0 to 9;

result_ge : out integer range 0 to 9;

q1_shi,q2_shi:out integer range 0 to 1;

q1_ge,q2_ge: out integer range 0 to 9);

end fenwei;

architecture a of fenwei is

--signal num1,num2:integer range 0 to 15;

--signal num1_shi ,num2_shi: integer range 0 to 1;

--signal num1_ge,num2_ge: integer range 0 to 9;

signal y_bai :integer range 0 to 2;

signal y_shi,y_ge :integer range 0 to 9;

signal temp :integer range 0 to 99; --中间变量

signal result: integer range 0 to 225 ;

begin

--num1<=q1;-----

--num2<=q2;-----

result<=y;

q1_shi <= 1 WHEN q1>9 ELSE

0 ;

q1_ge <= q1-10 WHEN q1>9 ELSE

q1 ;

q2_shi <= 1 WHEN q2>9 ELSE

0 ;

q2_ge <= q2-10 WHEN q2>9 ELSE

q2 ;

y_bai <=2 WHEN result>199 else

1 when result>99 else

0;

temp <= result-200 WHEN result>199 ELSE

result-100 WHEN result>99 ELSE

result;

y_shi<= 9 WHEN temp>89 ELSE

8 WHEN temp>79 ELSE

7 WHEN temp>69 ELSE

6 WHEN temp>59 ELSE

5 WHEN temp>49 ELSE

4 WHEN temp>39 ELSE

3 WHEN temp>29 ELSE

2 WHEN temp>19 ELSE

1 WHEN temp>9 ELSE

0 ;

y_ge<= temp-90 WHEN temp>89 ELSE

temp-80 WHEN temp>79 ELSE

temp-70 WHEN temp>69 ELSE

temp-60 WHEN temp>59 ELSE

temp-50 WHEN temp>49 ELSE

temp-40 WHEN temp>39 ELSE

temp-30 WHEN temp>29 ELSE

temp-20 WHEN temp>19 ELSE

temp-10 WHEN temp>9 ELSE

temp ;

--q1_shi<=num1_shi;

--q1_ge<=num1_ge;

--q2_shi<=num2_shi;

--q2_ge<=num2_ge;

result_bai<=y_bai;

result_shi<=y_shi;

result_ge<=y_ge;

end a;

显示模块:

LIBRARY IEEE;

USE IEEE.Std_Logic_1164.ALL;

USE IEEE.Std_Logic_Arith.ALL;

USE IEEE.Std_Logic_Unsigned.ALL;

ENTITY xianshi IS

PORT

(

result_bai: in integer range 0 to 2;

result_shi,result_ge,q1_ge,q2_ge:in integer range 0 to 9;

q1_shi,q2_shi:in integer range 0 to 1;

clk : IN STD_LOGIC;

led7: OUT STD_LOGIC_vector(7 downto 0);

sel_out: out STD_LOGIC_vector(6 downto 0)

);

END ;

ARCHITECTURE b OF xianshi IS

SIGNAL led0,led2: integer range 0 to 1;

signal led1,led3,led5,led6:integer range 0 to 9;

signal led4:integer range 0 to 2;

SIGNAL output : integer range 0 to 9;

BEGIN

led0<=q1_shi;

led1<=q1_ge;

led2<=q2_shi;

led3<=q2_ge;

led4<=result_bai;

led5<=result_shi;

led6<=result_ge;

scan:

PROCESS (clk)

VARIABLE count: integer range 0 to 6;

BEGIN

if (rising_edge(clk)) then

CASE count IS

WHEN 0 => output<=led6; sel_out<="1111110"; count:=1;

WHEN 1 => output<=led5; sel_out<="1111101"; count:=2;

WHEN 2 => output<=led4; sel_out<="1111011"; count:=3;

WHEN 3 => output<=led3; sel_out<="1110111"; count:=4;

WHEN 4 => output<=led2; sel_out<="1101111"; count:=5;

WHEN 5 => output<=led1; sel_out<="1011111"; count:=6;

WHEN 6 => output<=led0; sel_out<="0111111"; count:=0;

END CASE;

end if;

END PROCESS scan;

WITH output SELECT

led7 <= "00111111" WHEN 0,

"00000110" WHEN 1,

"01011011" WHEN 2,

"01001111" WHEN 3,

"01100110" WHEN 4,

"01101101" WHEN 5,

"01111101" WHEN 6,

"00000111" WHEN 7,

"01111111" WHEN 8,

"01101111" WHEN 9,

"10000000" WHEN OTHERS;

END b;

模块一:计算模块

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity jisuanqi is

Port (num1,num2: in integer range 0 to 15;

sel: in STD_LOGIC_VECTOR (1 downto 0);

y: out integer range 0 to 225);

end jisuanqi;

architecture rtl of jisuanqi is

signal q1 ,q2: integer range 0 to 15;

signal choice: STD_LOGIC_VECTOR (1 downto 0);

signal result: integer range 0 to 225;

begin

choice<=sel;

process(q1,q2,result,choice)

begin

case choice is

when "00" =>

result<=q1+q2;

when "01" =>

if(q1>q2)then

result <= q1-q2;

else

result<=q2-q1;

end if;

when "10"=>

result<=q1*q2;

when "11"=>

result<=0;

end case;

end process;

q1<=num1;

q2<=num2;

y <= result;

end rtl;

模块二:分为模块,将每个数字的位分离出来

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity fenwei is

Port (q1,q2: in integer range 0 to 15;

y :in integer range 0 to 225;

result_bai: out integer range 0 to 2;

result_shi: out integer range 0 to 9;

result_ge : out integer range 0 to 9;

q1_shi,q2_shi:out integer range 0 to 1;

q1_ge,q2_ge: out integer range 0 to 9);

end fenwei;

architecture a of fenwei is

--signal num1,num2:integer range 0 to 15;

--signal num1_shi ,num2_shi: integer range 0 to 1;

--signal num1_ge,num2_ge: integer range 0 to 9;

signal y_bai :integer range 0 to 2;

signal y_shi,y_ge :integer range 0 to 9;

signal temp :integer range 0 to 99; --中间变量

signal result: integer range 0 to 225 ;

begin

--num1<=q1;-----

--num2<=q2;-----

result<=y;

q1_shi <= 1 WHEN q1>9 ELSE

0 ;

q1_ge <= q1-10 WHEN q1>9 ELSE

q1 ;

q2_shi <= 1 WHEN q2>9 ELSE

0 ;

q2_ge <= q2-10 WHEN q2>9 ELSE

q2 ;

y_bai <=2 WHEN result>199 else

1 when result>99 else

0;

temp <= result-200 WHEN result>199 ELSE

result-100 WHEN result>99 ELSE

result;

y_shi<= 9 WHEN temp>89 ELSE

8 WHEN temp>79 ELSE

7 WHEN temp>69 ELSE

6 WHEN temp>59 ELSE

5 WHEN temp>49 ELSE

4 WHEN temp>39 ELSE

3 WHEN temp>29 ELSE

2 WHEN temp>19 ELSE

1 WHEN temp>9 ELSE

0 ;

y_ge<= temp-90 WHEN temp>89 ELSE

temp-80 WHEN temp>79 ELSE

temp-70 WHEN temp>69 ELSE

temp-60 WHEN temp>59 ELSE

temp-50 WHEN temp>49 ELSE

temp-40 WHEN temp>39 ELSE

temp-30 WHEN temp>29 ELSE

temp-20 WHEN temp>19 ELSE

temp-10 WHEN temp>9 ELSE

temp ;

--q1_shi<=num1_shi;

--q1_ge<=num1_ge;

--q2_shi<=num2_shi;

--q2_ge<=num2_ge;

result_bai<=y_bai;

result_shi<=y_shi;

result_ge<=y_ge;

end a;

显示模块:

LIBRARY IEEE;

USE IEEE.Std_Logic_1164.ALL;

USE IEEE.Std_Logic_Arith.ALL;

USE IEEE.Std_Logic_Unsigned.ALL;

ENTITY xianshi IS

PORT

(

result_bai: in integer range 0 to 2;

result_shi,result_ge,q1_ge,q2_ge:in integer range 0 to 9;

q1_shi,q2_shi:in integer range 0 to 1;

clk : IN STD_LOGIC;

led7: OUT STD_LOGIC_vector(7 downto 0);

sel_out: out STD_LOGIC_vector(6 downto 0)

);

END ;

ARCHITECTURE b OF xianshi IS

SIGNAL led0,led2: integer range 0 to 1;

signal led1,led3,led5,led6:integer range 0 to 9;

signal led4:integer range 0 to 2;

SIGNAL output : integer range 0 to 9;

BEGIN

led0<=q1_shi;

led1<=q1_ge;

led2<=q2_shi;

led3<=q2_ge;

led4<=result_bai;

led5<=result_shi;

led6<=result_ge;

scan:

PROCESS (clk)

VARIABLE count: integer range 0 to 6;

BEGIN

if (rising_edge(clk)) then

CASE count IS

WHEN 0 => output<=led6; sel_out<="1111110"; count:=1;

WHEN 1 => output<=led5; sel_out<="1111101"; count:=2;

WHEN 2 => output<=led4; sel_out<="1111011"; count:=3;

WHEN 3 => output<=led3; sel_out<="1110111"; count:=4;

WHEN 4 => output<=led2; sel_out<="1101111"; count:=5;

WHEN 5 => output<=led1; sel_out<="1011111"; count:=6;

WHEN 6 => output<=led0; sel_out<="0111111"; count:=0;

END CASE;

end if;

END PROCESS scan;

WITH output SELECT

led7 <= "00111111" WHEN 0,

"00000110" WHEN 1,

"01011011" WHEN 2,

"01001111" WHEN 3,

"01100110" WHEN 4,

"01101101" WHEN 5,

"01111101" WHEN 6,

"00000111" WHEN 7,

"01111111" WHEN 8,

"01101111" WHEN 9,

"10000000" WHEN OTHERS;

END b;

....哪里出问题了看哪部分代码...(吐槽 三点..1.养成多些注释的习惯.这样保证自己的思路清晰,方便检查.2.你的除法何在3.标志符最好用英文..拼音什么的很不舒服)还有你得给出尼的输入阿..输出是数码管显示.你的输入是用的按键还是拨盘 还是其他...

还有你的标志符 最好不要和专用词 重名

然后你的端口是否连接正确

谢谢分享

路过~正在做MUX8_1