BQ24171工作不正常问题

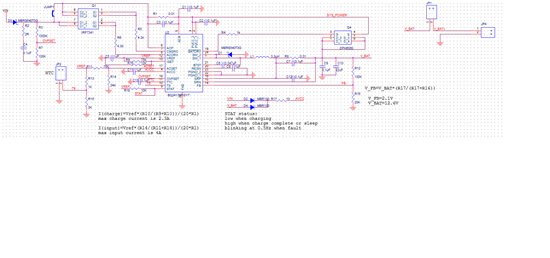

我在使用BQ24171的时候,出现了一个问题,BQ24171可以正常的工作给电池充电,电池是3节3.7V 18650型号的电池串联,但是当我断开外部电源的时候,BQ24171就不正常了,具体不工作的现象是Vref电压没有,请问这是为什么?贴图是原理图,其中Q1和Q4没有焊接,JUMP1短接。让我费解的是为什么不接外部电源的时候IC就不正常了,从而导致STAT脚在没有外部电源的时候测量一直是低电平。

你的电路图中AVCC只显示了一个旁路电容到地,没有看到AVCC是接输入源以外是否还有接BAT。

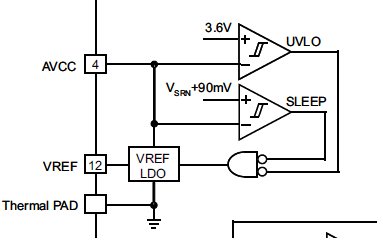

当芯片检测到ACVV小于SRN (输入源小于电池电压)时 会进入到sleep模式,禁止vref启动。

有兼容的呀,VAT和VIN是通过2个二极管兼容输出给AVCC的,附件的原理图也有画出来的啊,我看到datasheet上面AVCC会跟VSRN+90mv做比较,如果AVCC小于VSRN+90mv就会进入sleep,但是一般情况没有外部电源的话VBAT经过二极管衰减0.7V,肯定会比VSRN+90mv小的啊,所以我在外部电源断开后,我外接了一个板子上面其他的12V(VBAT升压得到的)给AVCC,Vref就有了,但是STAT还是一直是常低的,这个时候没有充电,STAT电平应该是高的才对的啊

抱歉,没有看到您电路图下方的标示。

在进入到sleep模式下 量测stat脚应该是高阻状态的。

你试试在用BAT做输入源时,测量STAT脚对地的电阻是否非常低,同时在将芯片完全掉电(AVCC不接BAT 不接充电器 也不接其他12V电压)的情况下,测量stat脚对地的阻抗,看看这个stat脚内部n-mosfet是否已经被击穿了。

在全部掉电的情况下,我测试了一下STAT管脚对地的阻抗大概是13K,不知道这个对不对?

掉电情况下 这个n-mosfet应该是没有导通的,所以其d-s阻抗(即stat脚对地阻抗)应该是相当于断路,所以应该是一个M欧姆级别的阻抗,你可以拿一个新的芯片测试一下芯片上stat脚与gnd脚之间的阻抗来验证一下。

仔细的检查stat脚周边的电路 看看是否有外部与stat脚的电路和器件拉低了这个阻值,比如stat脚是否有接外部的滤波电容,如果有接电容 看看电容的漏电流是否异常;是否接单片机的i/o口,如有接,看看是否i/o口有错误的下拉,等等

排除这一些因素以后,小心的将芯片从板子上焊下来以后 再测量STA脚对GND脚的阻抗,看看这个低阻抗到底是由芯片造成的还是外部电路造成的。如果量测到焊掉以后芯片本身的stat脚还是对地阻抗比较低,那么就说明芯片被损坏了,如果芯片焊掉以后量测正常,那么去量测pcb上芯片的stat脚焊盘与gnd的阻抗是否比较低,如果pcb板上阻值比较低,则仔细的检查是否板子上有污染,layout是否符合设计。

总结起来这个13K欧姆的电阻是你分析这个问题的突破点,小心谨慎的去试验,逐步找到真正的原因。

好的,那我去试试,谢谢了!

另外,这个STAT是开漏输出吗?

我看了一下我自己的电路,在STAT脚有一个pull-up电阻,去掉之后,stat对地的确是无穷大的,那是否说明stat脚正常了?

而且除了stat脚异常这个问题,我还发现在datasheet里面:AVCC小于VSRN+90mv的时候,IC会进入sleep模式,当没有外接电源的时候VBAT直连到AVCC也肯定小于VSRN+90mv=VBAT+90mv啊,那岂不是没有外部电源的时候IC就没法正常工作了?

是的,是开漏输出的结构。你提到的是pull up 还是pull donw?应该是有额外的pull down才符合现象。

这个ic是一个充电器ic,它的功能概括起来就是进行充电的调节和充电安全的相关保护,它并不管理电池放电的路径,所以不具备电池放电过程中的保护。所以如果电池不进行充电,那么就是在静止或放电状态,这都与充电时的状态无关,比如不会在放电时发生过压,输入电流过流的可能,所以芯片会sleep以避免额外的电流消耗,这是充电器芯片这样设计的目的。

电池组内部的充放电保护芯片还是不能省的,特别是在电芯串联比较高的情况下。此时充电器连接的电池实际上是一个包含内部保护芯片的电池包。

确定是pull-up,由于STAT是开漏结构所以我在外部加了pull-up,用来控制外部的LED来指示设备是否在充电。

关于sleep,我知道这个是为了低功耗的设计,但是sleep了,stat还能正常的输出高低电平来指示是否不在充电了呢?

datasheet中说:stat脚,低的时候在充电,高的时候没有充电或者sleep了,闪烁的时候指示出现故障。sleep了stat的功能是否还在?

如果sleep了,stat功能还保有的话,那就没什么了,但是如果sleep,stat的脚也关闭了,如何指示电池是否在充电呢?

由于stat是开漏输出,所以芯片需要上拉到vref,我没有在电路图中看到led元件,这是否意味着还有一部分电路没有在电路图上显示?即你指的上拉电阻是上拉到10k欧姆电阻,还是另外有上拉电路。如果有另外的上拉电路,那么当芯片进入sleep模式时这个上拉电路的上拉源是否还有电压,所以需要麻烦你把led部分的电路也附上来。

我仔细看了一下datasheet,AVCC如果直接从VBAT接过来的话会小于VSRN+90mv,所以在外部电源掉电后,IC肯定会进入sleep模式,这样的话我给stat用Vref做的pull-up就失去效果了,我试了一下用外部的电源作为stat的pull-up就发现stat在没有充电即外部电源掉电的时候是高电平。

我看参考电路设计VBAT连接到了AVCC还以为VBAT会成为IC的电源,其实这个时候是使IC进入sleep的,哎,纠结了好久原来是这个原因啊

进入sleep模式下,确实vref做的pull up失去了效果,但失去效果并不是说变为low, stat脚应该是高阻抗状态的,如果stat上有led灯, 那么此时led是不会亮的。

如果你用外部上拉源,当ref启动以后,ref与外部上拉源之间会存在倒灌的现象(如果两者有电压差)。

那我知道了,非常感谢,以后选芯片还是用TI的,呵呵!