关于TLV320ADC3001最低采样频率的疑问

http://www.ti.com/general/docs/lit/getliterature.tsp?genericPartNumber=tlv320adc3001&fileType=pdf

Supports ADC Sample Rates From 8 kHz to 96 kHz,在TLV320ADC3001手册首页中提示其采样频率为8kHz~96kHz。

但是在第40页:

Step 1

The system clock source (master clock) and the targeted ADC sampling frequency must be identified. Depending on the targeted performance, the decimation filter type (A, B, or C) and AOSR value can be determined:

Filter A should be used for 48-kHz high-performance operation; AOSR must be a multiple of 8.

Filter B should be used for up to 96-kHz operations; AOSR must be a multiple of 4.

Filter C should be used for up to 192-kHz operations; AOSR must be a multiple of 2.

In all cases, AOSR is limited in its range by the following condition: 2.8 MHz < AOSR *ADC_fS < 6.2 MHz

AOSR的取值范围是1~256,假设ADC_Fs=8kHz,8*256=2.048MHz,这不在2.8~6.2M的范围。

请TI解释一下吧

你好:

我是这样理解CLK问题的:

1.Filter A是用于48Khz采样频率的情况下,ASOR必须是8的倍数;

2.Filter B用于高达96Khz采样频率,ASOR必须是4的倍数;

3.同上

4.同时,AOSR的取值还受:2.8 MHz < AOSR *ADC_fS < 6.2 MHz条件的限制。

这四个条件都是限制ASOR的取值,所以应该根据合适的fs,取合适的ASOR。

假设ADC_Fs=8kHz,ASOR就不建议取256.

2.8 MHz < AOSR *ADC_fS < 6.2 MHz

咱们把公式变换下

2.8MHz/ADC_Fs<AOSR<6.2MHz/ADC_Fs

当ADC_Fs=8kHz

350<AOSR<775

而AOSR只能1~256!AOSR最大就是256了

请问如何才能得到8kHz的采样频率呢?还是不管这个公式2.8 MHz < AOSR *ADC_fS < 6.2 MHz?

你好,

关于datasheet中的描述,主要是针对于 filter A/B/C各自适应的场合来说的,filter A BC 分别 支持48K,96K,192K

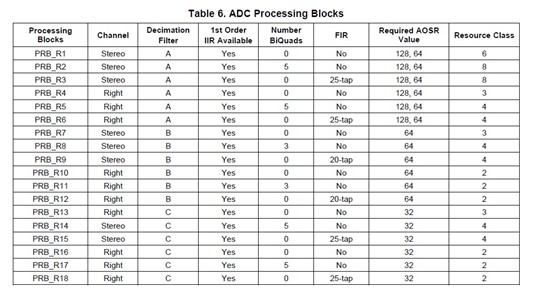

那么对于8K采样率分频参数的选取,取决于要使用哪一个PRB,对于相应的PRB,我们有推荐的AOSR值,以确保获得最好的性能。

比如使用PRB——R1,那AOSR推荐的值是128或者64,这是为了获得8K的采样率,需要调整其它分频参数

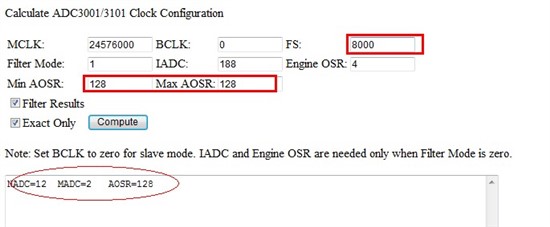

在AIC3101的GUI上,有一个工具来计算

比如选择AOSR 为128,采样率为8K,计算得结果如下: