aic3256的WCLK无法输出的问题

用另一个DSP的I2C对aic3256的寄存器进行读写,将其第一页的26号寄存器配置为0x80,27号寄存器为0x0d,29号寄存器为0x33,30号寄存器为0x80,(其它寄存器按照常规配置)

就是说BCKL_N开启,BCLK、WCLK都设为输出了。然后用示波器观察BCLK是正确的输出时钟,而WCLK却无输出且保持为低电平。请问为什么没有输出呢?难道还需要其它设置吗?

希望得到TI工程师们的关注,先谢为敬!

您好:

PLL部分您如何设置的?如果WCLK设为output,谁做为PLL的分频源?或者BCLK的时钟是从哪里来的?

可以将WCLK设为input,再将WCLK作为PLL的分频源,再向下分频给BCLK。

与CLK相关的寄存器如下,供参考:

| Register | Hex | Register Name | Reset Value | Current Value |

| Register 4 | 0x04 | Clock Setting Register 1, Multiplexers | 0x00 | 0x00 |

| Register 5 | 0x05 | Clock Setting Register 2, PLL P&R Values | 0x11 | 0x91 |

| Register 6 | 0x06 | Clock Setting Register 3, PLL J Values | 0x04 | 0x04 |

| Register 7 | 0x07 | Clock Setting Register 4, PLL D Values (MSB) | 0x00 | 0x00 |

| Register 8 | 0x08 | Clock Setting Register 5, PLL D Values (LSB) | 0x00 | 0x00 |

| Register 9 | 0x09 | Reserved | 0x00 | 0x00 |

| Register 10 | 0x0A | Reserved | 0x00 | 0x00 |

| Register 11 | 0x0B | Clock Setting Register 6, NDAC Values | 0x01 | 0x81 |

| Register 12 | 0x0C | Clock Setting Register 7, MDAC Values | 0x01 | 0x82 |

| Register 25 | 0x19 | Clock Setting Register 9, Multiplexers | 0x00 | 0x00 |

| Register 26 | 0x1A | Clock Setting Register 10, CLKOUT M divider value | 0x01 | 0x81 |

| Register 27 | 0x1B | Audio Interface Setting Register 1 | 0x00 | 0x00 |

| Register 28 | 0x1C | Audio Interface Setting Register 2, Data offset setting | 0x00 | 0x00 |

| Register 29 | 0x1D | Audio Interface Setting Register 3 | 0x00 | 0x00 |

| Register 30 | 0x1E | Clock Setting Register 11, BCLK N Divider | 0x01 | 0x81 |

你好,感谢关注!

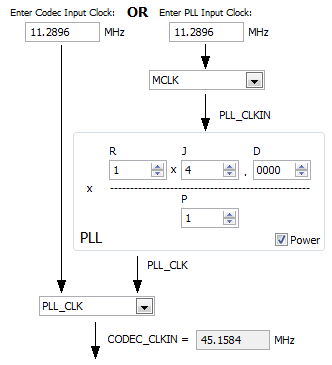

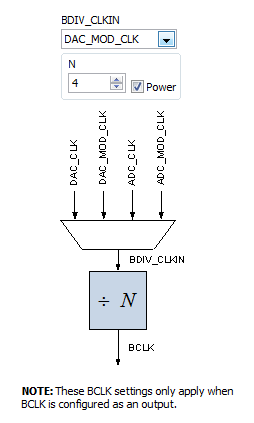

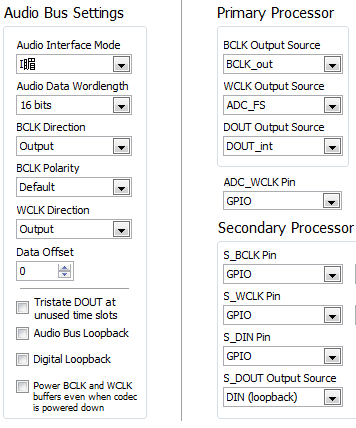

我是用MCLK(11.5MHz)作为PLL输入的(Page 0 Register 4 D3-D2=0x00),P、R、J、D、M、N的值也设置好了,BCLK的时钟(Bdiv_CLKIN)输入设置为ADC_MOD_CLK(Page 0 Register 30 D1-D0=0x11),BCLK N的值也设置并开启了。然后Page 0 Register 27 D3-D2=0x11,也就是BCLK和WCLK都设置为输出了。

现在的问题是BCLK有输出,并且能达到预期的频率,但是WCLK一直是低电平,为什么呢?

你好:

sorry for my late.

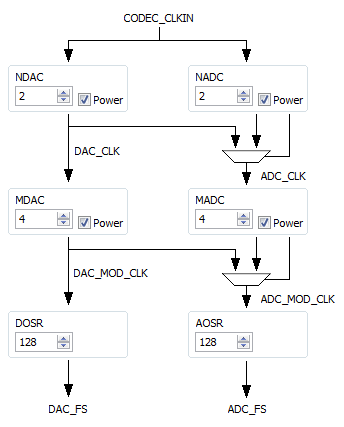

如果按照你这个思路设置,BCLK选用ADC_MOD_CLK,还需要设置AOSR,使ADC_FS=44.1K。然后注意选择WCLK的来源为ADC_FS。即page0 0x21寄存器为0x10。这样设置了,就可以得到MCLK得到的BCLK和WCLK。

按照你的配置:

3

相关寄存器配置:

| Register | Hex | Register Name | Reset Value | Current Value |

| Register 4 | 0x04 | Clock Setting Register 1, Multiplexers | 0x00 | 0x03 |

| Register 5 | 0x05 | Clock Setting Register 2, PLL P&R Values | 0x11 | 0x91 |

| Register 6 | 0x06 | Clock Setting Register 3, PLL J Values | 0x04 | 0x04 |

| Register 7 | 0x07 | Clock Setting Register 4, PLL D Values (MSB) | 0x00 | 0x00 |

| Register 8 | 0x08 | Clock Setting Register 5, PLL D Values (LSB) | 0x00 | 0x00 |

| Register 9 | 0x09 | Reserved | 0x00 | 0x00 |

| Register 10 | 0x0A | Reserved | 0x00 | 0x00 |

| Register 11 | 0x0B | Clock Setting Register 6, NDAC Values | 0x01 | 0x82 |

| Register 12 | 0x0C | Clock Setting Register 7, MDAC Values | 0x01 | 0x84 |

| Register 13 | 0x0D | DAC OSR Setting Register 1, MSB Value | 0x00 | 0x00 |

| Register 14 | 0x0E | DAC OSR Setting Register 2, LSB Value | 0x80 | 0x80 |

| Register 15 | 0x0F | DAC miniDSP instruction control Register 1 | 0x02 | 0x02 |

| Register 16 | 0x10 | DAC miniDSP instruction control Register 2 | 0x00 | 0x00 |

| Register 17 | 0x11 | DAC miniDSP Interpolation Factor Setting Register | 0x08 | 0x08 |

| Register 18 | 0x12 | Clock Setting Register 8, NADC Values | 0x01 | 0x82 |

| Register 19 | 0x13 | Clock Setting Register 9, MADC Values | 0x01 | 0x84 |

| Register 20 | 0x14 | ADC Oversampling (AOSR) Register | 0x80 | 0x80 |

| Register 21 | 0x15 | ADC miniDSP instruction control Register 1 | 0x01 | 0x01 |

| Register 22 | 0x16 | ADC miniDSP instruction control Register 2 | 0x00 | 0x00 |

| Register 23 | 0x17 | ADC miniDSP Decimation Factor Setting Register | 0x04 | 0x04 |

| Register 24 | 0x18 | Reserved Register | 0x00 | 0x00 |

| Register 25 | 0x19 | Clock Setting Register 9, Multiplexers | 0x00 | 0x00 |

| Register 26 | 0x1A | Clock Setting Register 10, CLKOUT M divider value | 0x01 | 0x01 |

| Register 27 | 0x1B | Audio Interface Setting Register 1 | 0x00 | 0x0C |

| Register 28 | 0x1C | Audio Interface Setting Register 2, Data offset setting | 0x00 | 0x00 |

| Register 29 | 0x1D | Audio Interface Setting Register 3 | 0x00 | 0x01 |

| Register 30 | 0x1E | Clock Setting Register 11, BCLK N Divider | 0x01 | 0x84 |

| Register 31 | 0x1F | Audio Interface Setting Register 4, Secondary Audio Interface | 0x00 | 0x00 |

| Register 32 | 0x20 | Audio Interface Setting Register 5 | 0x00 | 0x00 |

| Register 33 | 0x21 | Audio Interface Setting Register 6 | 0x00 | 0x10 |

| Register 34 | 0x22 | Digital Interface Misc. Setting Register | 0x00 | 0x00 |

| Register 35 | 0x23 | Reserved Register | 0x00 | 0x00 |

| Register 36 | 0x24 | ADC Flag Register | 0x00 | 0x00 |

| Register 37 | 0x25 | DAC Flag Register 1 | 0x00 | 0xEE |

| Register 38 | 0x26 | DAC Flag Register 2 | 0x00 | 0x11 |

这样配置在我们的EVM上是有时钟的,你check一下。

首先感谢你的耐心解答。

要不是看到你的回答,我都不知道该干什么了,现在问题解决了。

我把AOSR设置为256就行了,现在都能够回放声音了(不用旁通模式)。

现在的参数如下:J=8,M=8,AOSR=256,其它参数设置和你的一样,最后的采样率只有22kHz多一些,我输入的MCLK=13MHz左右。

也就是说以前的问题是:从BCLK一直有输出看来,ADC_MOD_CLK之前的时钟模块是没问题的,而原因是在于AOSR太小导致ADC_FS太高了?

你好,

可否把你的设置写出来,我是通过你的描述初步给了一个设定,但是我觉得不是完全设置的和你的一样。这样更方便找原因。

如果你用ADC的时钟那应该是采集吧,我门通常理解回放是指DAC工作。

设置时钟的时候需要先初步计算一下,对于格式是16bit的I2S,如果ADC_FS或者DAC_FS=44.1Khz,或者48K等常用的采样频率,那么WCLK就等于采样率,BCLK最小需要设置为2*16*44.1k=1.4112Mhz,所以如果选择ADC_MOD_CLK,需要根据ADC_MOD_CLK的值来选择分频系数N。或者前级的分频配合,保证BCLK>=2fs*16bit。

这样BCLK和MCLK就不会错。