紧急求助! 关于AIC3204的BCLK和WCLK输出的问题

TI的工程师您好!

我在使用AIC3204时遇到很奇怪的问题(AIC23B正常)。我希望配置3204为主模式,输出BCLK和WCLK, 使用了别的MCU, 控制程序用了usbstk5505的例程中的aic3204_loop_linein()和aic3204_tone_headphone( ),反复检查硬件,与usbstk5505完全一致。MCU操作I2C写3204成功,可看到正确应答信号。(如将地址改为别的,就没有应答,故判断MCU与3204应通信正常),MCLK用有源晶振10M, 但是我怎么也无法在BCLK和WCLK看到输出,已经调试1周无法解决,万望各位不吝赐教!程序如下,请帮忙看看是否有错误。以下主要是配置AIC3204,没有I2S数据收发部分。我理解只要配置完就应该在BCLK和WCLK测到输出波形,是这样吧?

Int16 aic3204_tone_headphone( )

{

Int16 j, i = 0;

Int16 sample;

I2C_Init(AIC3204_IDENT_W);

/* Configure Serial Bus */

//SYS_EXBUSSEL |= 0x0100; // Configure Serial bus 0 for I2S0

/* Configure AIC3204 */

if(!AIC3204_rset( 0, 0 ))return false; // Select page 0

AIC3204_rset( 1, 1 ); // Reset codec

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 1, 8 ); // Disable crude AVDD generation from DVDD

AIC3204_rset( 2, 1 ); // Enable Analog Blocks, use LDO power

AIC3204_rset( 0, 0 );

/* PLL and Clocks config and Power Up */

AIC3204_rset( 27, 0x0c ); // ori=d BCLK and WCLK are set as o/p; AIC3204(Master)

AIC3204_rset( 28, 0x00 ); // Data ofset = 0

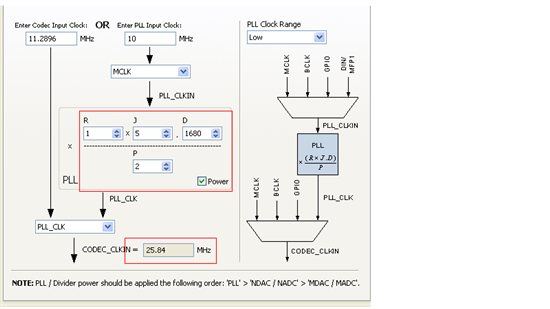

AIC3204_rset( 4, 3 ); // PLL setting: PLLCLK <- MCLK, CODEC_CLKIN <-PLL CLK

AIC3204_rset( 6, 5 ); // PLL setting: J=5;ORI=J=7

//AIC3204_rset( 7, 0x0 ); // PLL setting: HI_BYTE(D=0)

//AIC3204_rset( 8, 0x0 ); // PLL setting: LO_BYTE(D=0),

//AIC3204_rset( 7, 0x06 ); // PLL setting: HI_BYTE(D=1680)

//AIC3204_rset( 8, 0x90 ); // PLL setting: LO_BYTE(D=1680),

AIC3204_rset( 29, 0x80 );

AIC3204_rset( 30, 0x84 ); // For 32 bit clocks per frame in Master mode ONLY

// BCLK=DAC_CLK/N =(12288000/8) = 1.536MHz = 32*fs

AIC3204_rset( 5, 0xA1 ); // PLL setting:0XA1=P=2 and R=1; ORI=0X91=Power up PLL, P=1 and R=1

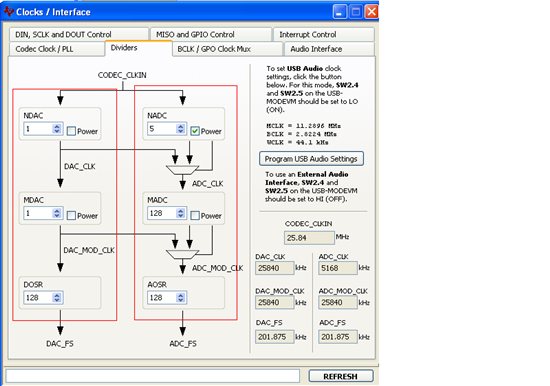

AIC3204_rset( 13, 0 ); // Hi_Byte(DOSR) for DOSR = 128 decimal or 0x0080 DAC oversamppling

AIC3204_rset( 14, 0x80 ); // Lo_Byte(DOSR) for DOSR = 128 decimal or 0x0080

AIC3204_rset( 20, 0x80 ); // AOSR for AOSR = 128 decimal or 0x0080 for decimation filters 1 to 6

AIC3204_rset( 11, 0x83 ); // Power up NDAC and set NDAC value to 3,ORI=2

AIC3204_rset( 12, 0x85 ); // Power up MDAC and set MDAC value to 5,ORI=7

AIC3204_rset( 18, 0x85 ); // Power up NADC and set NADC value to 5,ORI=7

AIC3204_rset( 19, 0x83 ); // Power up MADC and set MADC value to 3,ORI=2

/* DAC ROUTING and Power Up */

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 0x0c, 8 ); // LDAC AFIR routed to HPL

AIC3204_rset( 0x0d, 8 ); // RDAC AFIR routed to HPR

AIC3204_rset( 0, 0 ); // Select page 0

AIC3204_rset( 64, 2 ); // Left vol=right vol

AIC3204_rset( 65, 0); // Left DAC gain to 0dB VOL; Right tracks Left

AIC3204_rset( 63, 0xd4 ); // Power up left,right data paths and set channel

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 0x10, 0x00 );// Unmute HPL , 0dB gain

AIC3204_rset( 0x11, 0x00 );// Unmute HPR , 0dB gain

AIC3204_rset( 9, 0x30 ); // Power up HPL,HPR

AIC3204_rset( 0, 0 ); // Select page 0

//USBSTK5505_wait( 100 ); // wait

Delayms(100);

/* ADC ROUTING and Power Up */

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 0x34, 0x30 );// STEREO 1 Jack

// IN2_L to LADC_P through 40 kohm

AIC3204_rset( 0x37, 0x30 );// IN2_R to RADC_P through 40 kohmm

AIC3204_rset( 0x36, 3 ); // CM_1 (common mode) to LADC_M through 40 kohm

AIC3204_rset( 0x39, 0xc0 );// CM_1 (common mode) to RADC_M through 40 kohm

AIC3204_rset( 0x3b, 0 ); // MIC_PGA_L unmute

AIC3204_rset( 0x3c, 0 ); // MIC_PGA_R unmute

AIC3204_rset( 0, 0 ); // Select page 0

AIC3204_rset( 0x51, 0xc0 );// Powerup Left and Right ADC

AIC3204_rset( 0x52, 0 ); // Unmute Left and Right ADC

AIC3204_rset( 0, 0 );

//USBSTK5505_wait( 200 ); // Wait

Delayms(100);

}

你好:

我将你的代码数据放到我们的EVM板上测试,发现你的PLL与Divider设置有问题。

这个系数是你们需要的吗?并且没有power on divider。

还有就是你们的配置时序也有点问题。建议参考如下顺序:

--------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 1] = 0x01 ; Initialize the device through software reset

> 01

# --------------------------------------------------------------- page 1 is selected

w 30 00 01

# # reg[ 1][ 1] = 0x08 ; Disable weak AVDD to DVDD connection

> 08

# # reg[ 1][ 2] = 0x00 ; Enable Master Analog Power Control

> 00

# # reg[ 1][ 71] = 0x32 ; Set the input power-up time to 3.1ms

w 30 47 32

# # reg[ 1][123] = 0x05 ; Force REF charging time to 40ms

w 30 7b 05

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 5] = 0x91 ; P=1, R=1, J=24

w 30 05 91

# # reg[ 0][ 6] = 0x18 ; P=1, R=1, J=24

> 18

# # reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

> 00

# # reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

> 00

# # reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

w 30 04 03

# # reg[ 0][254] = 0x0a ; Delay 10ms for PLL to lock

w 30 fe 0a

# # reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

w 30 0c 88

# # reg[ 0][ 13] = 0x03 ; DOSR = 768 (MSB)

> 03

# # reg[ 0][ 14] = 0x00 ; DOSR = 768 (LSB)

> 00

# # reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

w 30 12 02

# # reg[ 0][ 19] = 0xb0 ; MADC = 48, divider powered on

> b0

# # reg[ 0][ 20] = 0x80 ; AOSR = 128

> 80

# # reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

w 30 0b 82

谢谢,问题解决。一是配置问题,另外是MCLK硬件连接问题,导致MCLK未送入。