PCM1808的输入模拟音频的范围

您好:

我最近在做一个多路语音切换的项目(其中包含两路语音叠加后从另一路输出),采用的方案是ADC+FPGA+DAC。ADC我选的是PCM1808,DAC选的是PCM1753,均采用左对齐方式。PCM1808的手册中说输入的模拟电压极限范围是-0.3V to (VCC+0.3V),实际的输入范围应该是1V-4V(以2.5V为中心,幅度3Vpp),但是在PCM1808EVM中,模拟信号进入PCM1808之前加了一个大电容,隔去了直流成分,变为了正负信号。我想问的是,是不是不管音频信号的直流电平是多少,只要加一个大的电容,即可接入PCM1808,而不必利用搬移电路将直流搬移到+2.5V。

你好:

是的,,但是前提要保证你的电容的耐压值大于你的直流信号加交流。你可以测下PCM1808的模拟输入点,会有偏置电压在那里。其次你的输入信号的Vpp不能超过PCM1808的供电电压Vcc否者会出现失真。

1.请问左对齐方式的数据串并转换后存起来就能直接播放吗,数据是补码形式吗,因为我们需要对语音进行存储然后回放,不知怎么处理,有没有相关的资料?

2.类似的AD和DA是不是都是双路的,最小都是24位吗(从TI的网站上看绝大多数音频ADC都是这样的),因为我们的时钟、数据都是母板间走线,需要尽量降低时钟的速率,2M的时钟母板间走线会有问题吗?多谢。

因为我们的语音信号输出和FPGA处理不在一块电路板上,之前的方案是将音频信号先转为平衡音频,在FPGA板上再转换回

非平衡音频,然后统一进行AD采样。为了省去中间的转换环节,考虑直接在模拟信号一侧进行AD采样,然后将串行数据通

过母板传到FPGA板,如果采用8K采样,系统时钟约2M,数据时钟约1M,不知可否通过母板直接传,如果不行,有没有推荐

的方案?多谢了

你好:

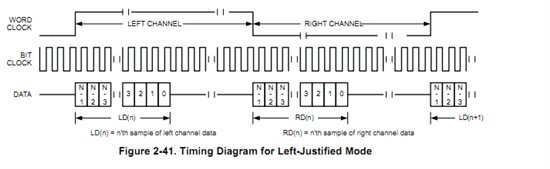

I2S的结构请看下图:

你可以在时钟的下降沿和上升沿分别保存左右声道的数据,然后输出的时候在合并成I2S的结构。或者直接用assign语句输出 bypass输出试下。它是PCM形式,并不是补码形式。

你现在使用的ADC最小时是24位的,但是也有些不是24位的。

如果你的走线不是很长,并且周围没有比较容易受干扰的信号就没关系。

你的母板到FPGA板子的线会很长吗?很长的话会影响你的音频信号的性能,比如信噪比等。如果对性能要求不高,直接传过去也没关系。

您好,有两个问题再向您请教一下:

1.对于PCM1754,如果想让其某个通道不输出声音,除了使用mute功能外,将其输入的数据一直置位0是不是也可以啊,或者就是不给时钟和数据。

2.下面的电路是将平衡音频转换为非平衡音频,从原理上看应该是对称电路,但是如果输入-10dBm的平衡音频,两个输入端的电压幅度分别为1.2V和0.4V,并且两个平衡输入的相位也不是完全相反的了。如果不接入我的电路,平衡音频两端的幅度均是0.8V,相位也完全相反。不知为何?

1.不给数据就可以无声,如果不给时钟,芯片会报错。

2.我没看到你的电路。还有就是两个输入端的电压幅度不同那就是非平衡的吧?

不知道我的理解对不对你是想把差分的信号转成单端的?

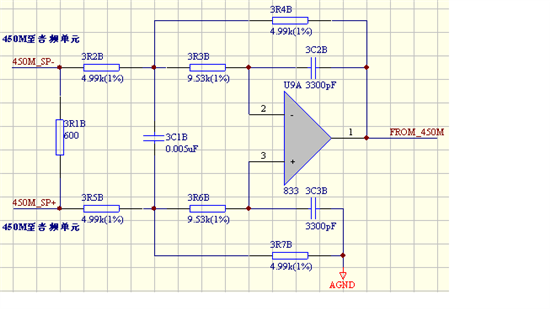

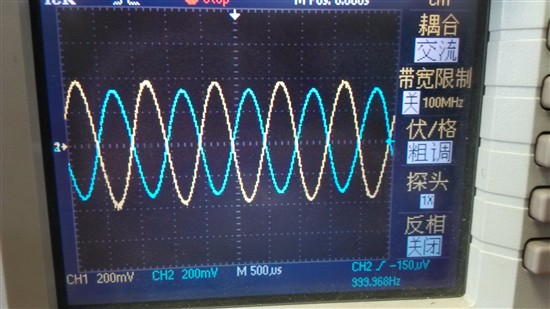

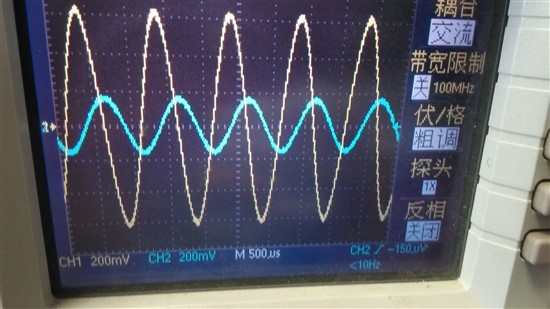

您好,以上是我的平衡音频转非平衡的电路,平衡音频未接入我的电路之前,两端的幅度相同,相位相反(如下面第一个图所示);但是接入到我的电路以后,再次测量450M_SP+和450M_SP-,两端幅度不相同,相位也不再完全相反了(如下面第二个图所示)。不知为什么?我的电路也是对称的啊。如果这样,那么就起不到差分的效果了,传输过程中有干扰的话也消除不了。

你好:

你把那个600ohm的电阻拿掉看下。

此链接是我们的一颗DRV632的差分转单端的原理图,你可以借鉴下。

http://www.ti.com/lit/ug/slou301/slou301.pdf

您好,上次的问题一直没有解决。我看了DRV632的电路图,和我们的基本一样啊。我们又参考了PCM3168A手册中的图63电路,也是一样的。我们的运放换过LM833D和SA5532,输入信号是两路幅度相同、相位相反的平衡音频信号,无直流成分,双极性。但是实测的时候发现输入信号加到电路上后,输入端原来的幅度相同的平衡信号现在幅度变得不一样了。使用LM833D时两路信号相差6倍以上,而且相位有点偏移;使用SA5532时两路信号相差2倍左右,相位无变化。两种芯片效果不太一样,不知和芯片有没有关系。

电路原理应该没问题啊,不知何故。

你好:

你把左右的输入换下,就是把左接到右,右接到左,看下是不是和你之前观察的一样,我觉得是你一个通道的电阻电容可能焊错了。建议你仔细检查下。并且你的一个通道出来的频率不会。

您好,把左右的输入交换后没有变化,通道的电阻也不可能焊错,因为每个通道都是这样,而且不止一种电路板。

后来我又详细测试了一下,发现最终差分转单端的放大倍数还是和设计一样的,只是相位有些偏移。但最主要的问题还是两个输入信号的幅度会变化,一个大一个小,约相差4倍左右。我同事用multisim仿真了一下,发现和实际的情况一样,输入信号幅度会变化。

我看TI的好多datasheet中都推荐了这种电路,不知是否都有这种问题,还请多多帮忙咨询一下。

另外,看见有的电路在差分信号输入之前分别都加了一级运放,见附件,均是同相端输入,说是为了提高输入电阻,原来差分信号直接进后一级运放的话可能输入电阻比较小,不知有无影响。

你好:

我仿真了一下你的电路并没有问题,你在前级输出的时候加隔直电容了吗?建议加个试一下。