当AIC3104启用ADC时产生很大的白噪声底噪,但经过PGA后直接输出的音频没有听到任何底噪(是否要经effects滤波后再输出I2S?)

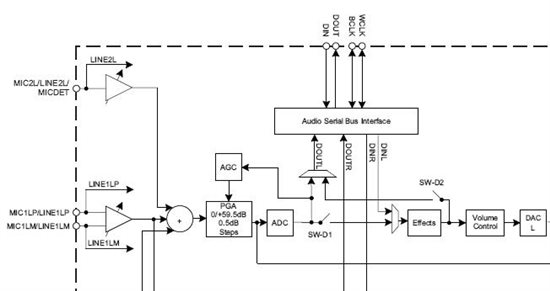

麦克风从MIC2R输入,内部连接到左右声道,经过PGA 0db 放大后 音频直接输出到HPROUT端口监听,同时音频经过ADC输出数字信号。

另一端接收到ADC数据后还原后播放。 从HPROUT直接监听的音频没有底噪,经过ADC采样后的音频存在很大的底噪声。如果将PGA power down后,ADC的底噪消失。如果直接断开所有的音频输入端,只启动内部PGA 和 ADC 底噪仍然存在。

相关寄存器配置如下:

_WrData(0,0x00);

_WrData(1,0x80);//reset

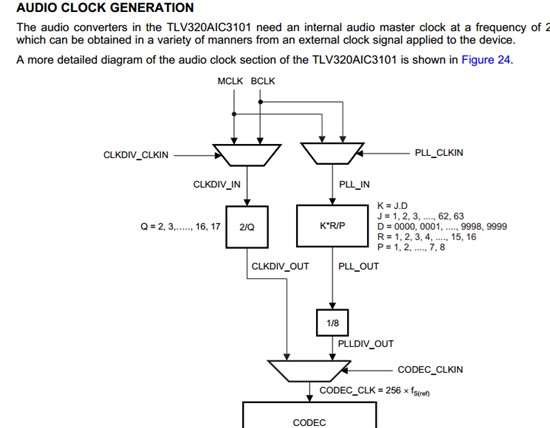

_WrData(3,0x10);//PLL is disabled, Q = 2.

_WrData(101,0x01);//clock use clkdiv_out

_WrData(102,0x02);//use MCLK

_WrData(7,0x8A);//AGC time constant fs=44.1Khz, left-DAC play left-channel input data, right-DAC play right-channel.

_WrData(9,0);//I2S mode. 16bit

_WrData(25,0x80);//MICBIAS 2.5V

_WrData(19,0x7C);//power up left ADC

_WrData(26,0x80);//enable left AGC

_WrData(17,0xf0);//MIC2R connect to left ADC

_WrData(15,0x0a);//left ADC PGA not mute,5db(0~59.5db)(增益可调)(x1111111)

_WrData(27,0x14);//left AGC gain 5db(0~59.5db)(可调)(与ADC增益一致)(1111111x)

_WrData(22,0x7c);//power up right ADC

_WrData(29,0x80);//enable right AGC

_WrData(18,0xf0);//MIC2R connect to right ADC

_WrData(16,0x0a);//left ADC PGA not mute,5db(0~59.5db)(增益可调)(x1111111)

_WrData(30,0x14);//left AGC gain 5db(0~59.5db)(可调)(与ADC增益一致)(1111111x)

_WrData(37,0x20);//power down left/right DAC, HPLCOM as single-end

_WrData(107,0x08);//ADC digital output to programmable filter path

_WrData(65,0x0d);//HPROUT level 0db(0~9db), unmute HPROUT,HPROUT power up

_WrData(63,0x80);//PGA_R to HPROUT, 0db(0db~-78.3db)(可调)

你好:

需要你换个顺序,在配置完后再打开左右ADC的power,如果打开power再配置会出问题。

还有测试下I2S的时钟是否和你们配置的一致。

您好Derek,

我根据您的方法换了个顺序,配置完再打开ADC的POWER,但是问题依旧。I2S时钟已经测试过,是正常的。与配置一致。

我看到有些CODEC,例如UDA1341,输出时有一些滤波filter和NOISE SHAPER,对于TI的3104,我有看到EFFECTS是可以接到ADC后面再输出的。

我想问:在ADC后面,是否还需要打开EFFECT进行一些相关的操作,使噪声消除掉? 或者还有一些其他的原因吗?

你好:

理论上不打开effect filter噪声也能被滤除一点,这个是Delta sigma ADC的一个特点。你的晶振是12M,但是我没有看到你配置了PLL来满足你的采样率。

你试下关闭AGC试下。看看是不是AGC的影响,把增益调的太大了。

Hi Derek

我在这个应用中3104作为从设备,没有用12Mhz的晶振输入。我用一颗STM32的主控IC 输出256fs(fs=44.1k)输入到MCLK, 内部分频使用CLKdiv_IN, Q=2, 所以直接到CODEC的CODEC_CLK=MCLK=256fs, 实际内部没有作分频,直接由STM32提供采样时钟。具体配置为

_WrData(3,0x10);//PLL is disabled, Q = 2.

_WrData(101,0x01);//clock use clkdiv_out

_WrData(102,0x02);//use MCLK

_WrData(7,0x8A);//AGC time constant fs=44.1Khz, left-DAC play left-channel input data, right-DAC play right-channel.

而且AGC我也偿试关闭过,PGA和AGC的增益我也试过调到0db输入。但只要一启动PGA,这个白噪声就会出现,非常明显。但经过PGA直接输出到HPROUT端监听却很干净,所以我一直怀疑ADC部分是否有什么问题?不知道其他人有没有出现类似的情况。

你好:

你的主控的时钟和AIC3105的同步么?建议还是用晶振的时钟。

你好,

跟AIC3105连接是另外一种应用, 在这个应用中没有使用AIC3105, 只是主控MCU(使用STM32F107)作为I2S主设备,输出BCLK, WCLK到AIC3104, 并输出256fs(fs = 44.1k)的频率到AIC3104的MCLK端, AIC3104内部没作分频直接作为CODEC的时钟,即256fs. 你的意思是提供给AIC3104的时钟的误差产生噪音?还是我需要使用外部12Mhz 晶振 作为MCLK的输入时钟,让AIC3104分频? 这个ADC白噪声产生的原因是什么呢? 采样频率应该是比较标准的,因为我使用其它的DAC芯片能成功还原出来声音。

你好:

如果你的MCU即提供了I2S的时钟又提供MCLK吗? 你给AIC3104的MCLK要内部产生让芯片工作的时钟。这个时钟要和你的采样率一致。不一致会产生噪声。

还有就是你的MCU的格式和采样的格式是否也是一致的。你可以Bypss你的MCU,直接用我的Codec采集加播放看是否还有噪声。

Hi Derek,

我想问:MCU提供给AIC3104的I2S MCLK是否需要很准?允许的偏差是多少?因为我们现在使用的MCU提供的采样率大约会比44.1K稍微低一些,大概是43点多。这个是否会影响AIC3104的ADC采样?

因为MCU是主,AIC3104是从,如果MCU有这种采样偏差,AIC3104是否能通过某些配置能容忍这种偏差?

除了MCU采样频率的一点偏差外,采样深度和格式都是OK的。

你好:

你的AIC3104的MCLK是谁提供的?如果和MCU的I2S不是同源的,那时钟就是不同步的。

建议使用BCLK来当AIC3104中主时钟的信号源,来产生AIC3104内部的时钟这样就没有不同步的问题。