AIC3254 启动问题与延时调节功能实现过程

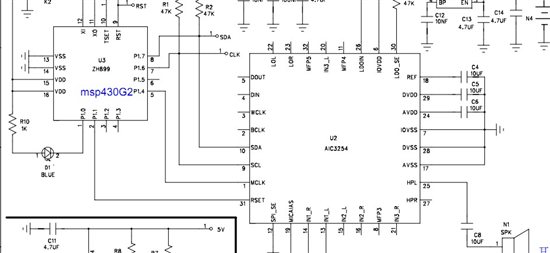

AIC3254 启动问题 :没有IIS,时钟是用MSP430产生的8M给AIC3254工作时钟的,但是每次启动要用手摸一下MCLK才能启动,什么原因呢!大侠们能否说明一下AIC3254启动过程。

另外需要功能调节延时,请问怎么实现? 目前已经实现固定的延时。谢谢!

你好:

AIC3254的启动过程可参考附件的第87页和txt文档2555.AIC3254.txt。2671.TLV320AIC3254RG.pdf

你说的这种情况很奇怪,但是通常是由于配置AIC3254不正确所导致。请问你是如何配置AIC3254的?

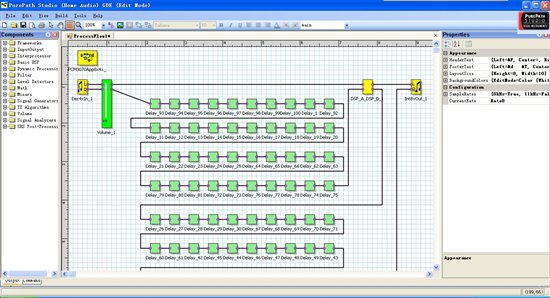

此外你说的需要功能调节延时是需要用在哪里?您说在固件中的延迟已经实现是说Pure Path Studio中实现么?

HI Derek

如何配置AIC3254,是由Pure Path Studio 产生main_Rate8.cfg ,按main_Rate8.cfg里面的顺序写命令的。

另外MSP430写程序,这p1.1接AIC3254 的RESET引脚,P1.4产生一个8M的时钟给AIC3254给 MCLK 引脚。请问这两个引脚操作有什么注意的、?

此外你说的需要功能调节延时是需要用在哪里?您说在固件中的延迟已经实现是说Pure Path Studio中实现么?

补充:调节延时功能是MIC 的声音到耳机输出的延时,这样效果可助听器类似,外接一个按键做调节。 固定的延迟在Pure Path Studio中实现了,但是将更改为MCU+AIC3254自己做的PCB小板上出现用手接触一下才能有声音输出。暂时没有找到原因在哪,急急急!

你好:

由于Purepath下载后,会把Codec配置成默认的格式。他对PLL的配置的分频系数是按照MCLKC为4.096M的配置。并且会配置Codec为从模式。请问你的系统中,I2S时钟是外部提供的,还是Codec自己产生的。如果是外部提供仅需要修改AIC3254的分频器和PLL的配置。如果是自己产生,还需要将Codec配置从主模式,Power on BCLK。

你好:

如果是MIC进,Headphone出,那么Codec是主。

如图,codec 时钟是 MCU产生8M 给MCLK

如图,codec 时钟是 MCU产生8M 给MCLK

配置如下:

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 1] = 0x01 ; Initialize the device through software reset

> 01

# --------------------------------------------------------------- page 1 is selected

w 30 00 01

# # reg[ 1][ 1] = 0x08 ; Disable weak AVDD to DVDD connection

> 08

# # reg[ 1][ 2] = 0x00 ; Enable Master Analog Power Control

> 00

# # reg[ 1][ 71] = 0x32 ; Set the input power-up time to 3.1ms

w 30 47 32

# # reg[ 1][123] = 0x05 ; Force REF charging time to 40ms

w 30 7b 05

# --------------------------------------------------------------- page 8 is selected

省略中间 一起写完

# --------------------------------------------------------------- page 166is selected

后面再写配置

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 60] = 0x00 ; Use miniDSP_D for signal processing

w 30 3c 00

# # reg[ 0][ 61] = 0x00 ; Use miniDSP_A for signal processing

> 00

# # reg[ 0][ 17] = 0x08 ; 8x Interpolation

w 30 11 08

# # reg[ 0][ 23] = 0x04 ; 4x Decimation

w 30 17 04

#

w 30 0f 03

#

> 88

#

w 30 15 03

#

> 88

# --------------------------------------------------------------- page 8 is selected

w 30 00 08

# # reg[ 8][ 1] = 0x04 ; adaptive mode for ADC

> 04

# --------------------------------------------------------------- page 44 is selected

w 30 00 2c

# # reg[ 44][ 1] = 0x04 ; adaptive mode for DAC

> 04

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 5] = 0x91 ; P=1, R=1, J=24

w 30 05 91

# # reg[ 0][ 6] = 0x18 ; P=1, R=1, J=24

> 18

# # reg[ 0][ 7] = 0x00 ; D=0000 (MSB)

> 00

# # reg[ 0][ 8] = 0x00 ; D=0000 (LSB)

> 00

# # reg[ 0][ 4] = 0x03 ; PLL_clkin = MCLK, codec_clkin = PLL_CLK, PLL on

w 30 04 03

# # reg[ 0][254] = 0x0a ; Delay 10ms for PLL to lock

w 30 fe 0a

# # reg[ 0][ 12] = 0x88 ; MDAC = 8, divider powered on

w 30 0c 88

# # reg[ 0][ 13] = 0x03 ; DOSR = 768 (MSB)

> 03

# # reg[ 0][ 14] = 0x00 ; DOSR = 768 (LSB)

> 00

# # reg[ 0][ 18] = 0x02 ; NADC = 2, divider powered off

w 30 12 02

# # reg[ 0][ 19] = 0xb0 ; MADC = 48, divider powered on

> b0

# # reg[ 0][ 20] = 0x80 ; AOSR = 128

> 80

# # reg[ 0][ 11] = 0x82 ; NDAC = 2, divider powered on

w 30 0b 82

# --------------------------------------------------------------- page 1 is selected

w 30 00 01

# # reg[ 1][ 51] = 0x40 ; Mic Bias enabled, Source = Avdd, 1.25V

w 30 33 40

# # reg[ 1][ 52] = 0x40 ; Route IN1L to LEFT_P with 10K input impedance

> 40

# # reg[ 1][ 54] = 0x40 ; Route CM1L to LEFT_M with 10K input impedance

w 30 36 40

# # reg[ 1][ 55] = 0x40 ; Route IN1R to RIGHT_P with 10K input impedance

> 40

# # reg[ 1][ 57] = 0x40 ; Route CM1R to RIGHT_M with 10K input impedance

w 30 39 40

# # reg[ 1][ 59] = 0x00 ; Enable MicPGA_L Gain Control, 0dB

w 30 3b 00

# # reg[ 1][ 60] = 0x00 ; Enable MicPGA_R Gain Control, 0dB

> 00

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 81] = 0xc0 ; Power up LADC/RADC

w 30 51 c0

# # reg[ 0][ 82] = 0x00 ; Unmute LADC/RADC

> 00

# --------------------------------------------------------------- page 1 is selected

w 30 00 01

# # reg[ 1][ 20] = 0x25 ; De-pop: 5 time constants, 6k resistance

w 30 14 25

# # reg[ 1][ 12] = 0x08 ; Route LDAC to HPL

w 30 0c 08

# # reg[ 1][ 13] = 0x08 ; Route RDAC to HPR

> 08

# # reg[ 1][ 14] = 0x08 ; Route LDAC to LOL

> 08

# # reg[ 1][ 15] = 0x08 ; Route LDAC to LOR

> 08

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 63] = 0xd4 ; Power up LDAC/RDAC w/ soft stepping

w 30 3f d4

# --------------------------------------------------------------- page 1 is selected

w 30 00 01

# # reg[ 1][ 16] = 0x00 ; Unmute HPL driver, 0dB Gain

w 30 10 00

# # reg[ 1][ 17] = 0x00 ; Unmute HPR driver, 0dB Gain

> 00

# # reg[ 1][ 18] = 0x00 ; Unmute LOL driver, 0dB Gain

> 00

# # reg[ 1][ 19] = 0x00 ; Unmute LOR driver, 0dB Gain

> 00

# # reg[ 1][ 9] = 0x3c ; Power up HPL/HPR and LOL/LOR drivers

w 30 09 3c

# --------------------------------------------------------------- page 0 is selected

w 30 00 00

# # reg[ 0][ 64] = 0x00 ; Unmute LDAC/RDAC

w 30 40 00

# # reg[0][82] = 0

w 30 52 00

# # reg[0][83] = 0

> 00

# # reg[0][86] = 32

w 30 56 20

# # reg[0][87] = 223

> df

# # reg[0][88] = 0

> 00

# # reg[0][89] = 104

> 68

# # reg[0][90] = 168

> a8

# # reg[0][91] = 6

> 06

# # reg[0][92] = 0

> 00

# # reg[0][84] = 0

w 30 54 00

# # reg[0][94] = 32

w 30 5e 20

# # reg[0][95] = 223

> df

# # reg[0][96] = 0

> 00

# # reg[0][97] = 104

> 68

# # reg[0][98] = 168

> a8

# # reg[0][99] = 6

> 06

# # reg[0][100] = 0

> 00

你好:

PPS 中的cfg配置是针对MCLK为4.096MCLK配置的,并且是从模式。现在您需要修改时钟和I2S格式,Codec的PLL中的系数R ,J, D,P. Dividers中的NDAC, NADC MDAC,MADC,DSOR,ASOR。 I2S 接口配置BCLK direction, WCLK direction, Bdiv_CLKIN.

能否详细说明一下,如上怎样改正?

你好:

PLL修改该三个寄存器:

# # reg[ 0][ 6] = 0x0C ; P=1, R=1, J=12

w 30 06 0C

# # reg[ 0][ 7] = 0x0B ; D=2880 (MSB)

w 30 07 0B 40

# # reg[ 0][ 8] = 0x40 ; D=2880 (LSB)

I2S格式需要修改的寄存器:

# # reg[ 0][ 27] = 0x0C ; BCLK and WCLK Output

w 30 1B 0C

# # reg[ 0][ 29] = 0x01 ; Bdiv_CLKIN = DAC_MOD_CLK

w 30 1D 01

# # reg[ 0][ 30] = 0x8C ; Power ON BCLK Divider

w 30 1E 8C

谢谢Derek 问题已经解决!

DEREK 您好!

打扰您!我在使用AIC3204时遇到很奇怪的问题。我希望配置3204为主模式,输出BCLK和WCLK, 使用了别的MCU, 控制程序用了usbstk5505的例程中的aic3204_loop_linein()和aic3204_tone_headphone( ),反复检查硬件,与usbstk5505完全一致。MCU操作I2C写3204成功,可看到正确应答信号。(如将地址改为别的,就没有应答,MCU与3204应通信正常),MCLK用有源晶振10M, 但是我怎么也无法在BCLK和WCLK看到输出,已经调试1周无法解决,万望不吝赐教!程序如下:

Int16 aic3204_tone_headphone( )

{

Int16 j, i = 0;

Int16 sample;

//if(!I2C_Init(AIC3204_IDENT_W)) //Write CMD addr=0x34,aic23 addrs

//{return false;}

//IdentAddr =0x30;

I2C_Init(AIC3204_IDENT_W);

/* Configure Serial Bus */

//SYS_EXBUSSEL |= 0x0100; // Configure Serial bus 0 for I2S0

/* Configure AIC3204 */

if(!AIC3204_rset( 0, 0 ))return false; // Select page 0

AIC3204_rset( 1, 1 ); // Reset codec

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 1, 8 ); // Disable crude AVDD generation from DVDD

AIC3204_rset( 2, 1 ); // Enable Analog Blocks, use LDO power

AIC3204_rset( 0, 0 );

/* PLL and Clocks config and Power Up */

AIC3204_rset( 27, 0x0c ); // ori=d BCLK and WCLK are set as o/p; AIC3204(Master)

AIC3204_rset( 28, 0x00 ); // Data ofset = 0

AIC3204_rset( 4, 3 ); // PLL setting: PLLCLK <- MCLK, CODEC_CLKIN <-PLL CLK

AIC3204_rset( 6, 5 ); // PLL setting: J=5;ORI=J=7

//AIC3204_rset( 7, 0x0 ); // PLL setting: HI_BYTE(D=0)

//AIC3204_rset( 8, 0x0 ); // PLL setting: LO_BYTE(D=0),

//AIC3204_rset( 7, 0x06 ); // PLL setting: HI_BYTE(D=1680)

//AIC3204_rset( 8, 0x90 ); // PLL setting: LO_BYTE(D=1680),

//NOW J.D=5.0, PLL=36.864M/2*5=92.16M,ADC_MOD_CLK=92.16M/15=6.144M, /128=48KHZ

//ORI= J.D=7.168, PLL=12M*7.168=86.016M,ADC_MOD_CLK=86.016M/14=6.144M, /128=48KHZ

AIC3204_rset( 29, 0x80 );

AIC3204_rset( 30, 0x84 ); // For 32 bit clocks per frame in Master mode ONLY

// BCLK=DAC_CLK/N =(12288000/8) = 1.536MHz = 32*fs

AIC3204_rset( 5, 0xA1 ); // PLL setting:0XA1=P=2 and R=1; ORI=0X91=Power up PLL, P=1 and R=1

AIC3204_rset( 13, 0 ); // Hi_Byte(DOSR) for DOSR = 128 decimal or 0x0080 DAC oversamppling

AIC3204_rset( 14, 0x80 ); // Lo_Byte(DOSR) for DOSR = 128 decimal or 0x0080

AIC3204_rset( 20, 0x80 ); // AOSR for AOSR = 128 decimal or 0x0080 for decimation filters 1 to 6

AIC3204_rset( 11, 0x83 ); // Power up NDAC and set NDAC value to 3,ORI=2

AIC3204_rset( 12, 0x85 ); // Power up MDAC and set MDAC value to 5,ORI=7

AIC3204_rset( 18, 0x85 ); // Power up NADC and set NADC value to 5,ORI=7

AIC3204_rset( 19, 0x83 ); // Power up MADC and set MADC value to 3,ORI=2

/* DAC ROUTING and Power Up */

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 0x0c, 8 ); // LDAC AFIR routed to HPL

AIC3204_rset( 0x0d, 8 ); // RDAC AFIR routed to HPR

AIC3204_rset( 0, 0 ); // Select page 0

AIC3204_rset( 64, 2 ); // Left vol=right vol

AIC3204_rset( 65, 0); // Left DAC gain to 0dB VOL; Right tracks Left

AIC3204_rset( 63, 0xd4 ); // Power up left,right data paths and set channel

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 0x10, 0x00 );// Unmute HPL , 0dB gain

AIC3204_rset( 0x11, 0x00 );// Unmute HPR , 0dB gain

AIC3204_rset( 9, 0x30 ); // Power up HPL,HPR

AIC3204_rset( 0, 0 ); // Select page 0

//USBSTK5505_wait( 100 ); // wait

Delayms(100);

/* ADC ROUTING and Power Up */

AIC3204_rset( 0, 1 ); // Select page 1

AIC3204_rset( 0x34, 0x30 );// STEREO 1 Jack

// IN2_L to LADC_P through 40 kohm

AIC3204_rset( 0x37, 0x30 );// IN2_R to RADC_P through 40 kohmm

AIC3204_rset( 0x36, 3 ); // CM_1 (common mode) to LADC_M through 40 kohm

AIC3204_rset( 0x39, 0xc0 );// CM_1 (common mode) to RADC_M through 40 kohm

AIC3204_rset( 0x3b, 0 ); // MIC_PGA_L unmute

AIC3204_rset( 0x3c, 0 ); // MIC_PGA_R unmute

AIC3204_rset( 0, 0 ); // Select page 0

AIC3204_rset( 0x51, 0xc0 );// Powerup Left and Right ADC

AIC3204_rset( 0x52, 0 ); // Unmute Left and Right ADC

AIC3204_rset( 0, 0 );

//USBSTK5505_wait( 200 ); // Wait

Delayms(100);

}