调试DRV8301时,遇到的几个问题

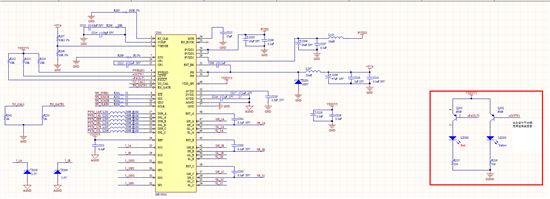

1、使用过程中感觉DRV8301极其的脆弱,感觉非常容易损坏。参照官方推荐的电路设计了PCB,自己焊接了两块,交由专业焊接公司机贴了两块,自己焊接的两块板子上4片DRV8301(每块板子有使用两片DRV8301)全部损坏,焊接公司焊接的两块板子中也有一片DRV8301上电初始化后一直告警欠压(GVDD_UV);

2、当电源电压低于24V时,芯片就工作不正常,无法驱动电机(电机额定工作电压为36V);

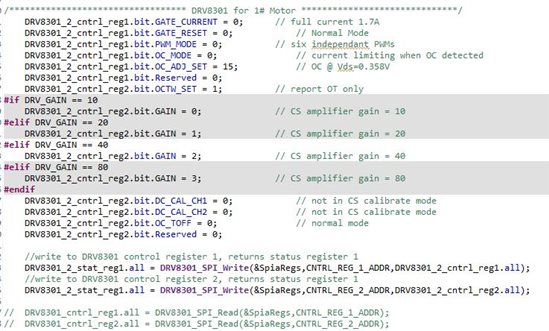

3、过流保护不起作用,将8301内部OC_ADJ_SET寄存器设置为20时,启动电机,发现将DRV8301损坏了,而MOSFET却都正常,根据外部运放设计的检测回路,实际也没有到达预设保护的电流值;

4、当给DRV8301初始化时,发现SDO引脚输出的信号一直为高电平,无法读出数据;

5、当PCB板驱动同时两路电机时,其中的一片DRV8301会频繁告警,其状态寄存器的GVDD_OV、PVDD_UV、GVDD_UV、OTW、OSTD、FAULT同时为1,但是电机能够正常转动。

以上现象都是在同样的PCB板子上的实验。

您好!

能不能把损坏的DRV8301检查下看看是哪个部分损坏了?

我这边有12V供电的,工作都正常,这个要看一下原理图了。

其他的问题,请把原理图以及程序配置部分贴出来。

各个损坏的片子的情况不一样。一片是SPI的4个管脚与GND短接(拆下芯片后,测量芯片管脚);

一片是上电后,使能EN_GATE引脚后,nFAULT引脚为低电平,但是与其通信SPI通信引脚的SDO引脚一直为高电平,驱动不了电机;

剩下的几片是上电后nFAULT引脚为低电平,通信都正常,但是初始化配置寄存器后,nFAULT引脚还是为低电平,查看其状态寄存器,告警位为GVDD_UV、PVDD_UV;

目前能够正常工作的芯片,在电源电压低于24V时,8301就不正常工作。

如果是电源电压低时不能正常工作,很有可能是去耦电容不够或者摆放不对,不够靠近PVDD以及半桥顶点。几个逻辑和模拟的低压电源口也要摆放好去耦电容,确保瞬时大电流工作时各个电压的稳定性,尤其是PVDD DVDD 请仔细参考DRV8301 boostpack 的版图设计和电容放置, 还有就是芯片底部焊盘一定要焊接好到地,必要条件,而且手工很难焊接好

您好!

针对于DRV8301的Layout设计,我想咨询一下下面几个问题。

1、请问DRV8301芯片要与半桥的离得很近吗?(我们现在DRV8301和桥电路是分开在两块板子上的,中间用排针连接,板子上走线也较长);

2、去耦电容是要靠近DRV8301的芯片引脚还是要尽量靠近半桥顶点?

3、去耦电容容值比推荐电路要大,对DRV8301,没有影响吧?

4、使用DRV8301时,PVDD1和PVDD2之间接有一个二极管,不影响DRV8301的使用吧?

1. 这是个比较严重的问题,主要是芯片的电流保护监测是监测mos的Vds,这样会造成很大的寄生干扰信号,尤其是PVDD端,去耦电容放好会改善

2. 最好是DRV8301PVDD有独立的去耦电容,可以参考EVM和boostpack的设计,这个电容不用太大,到10u,再并联小的陶瓷0.1就可以了。每个半桥顶点的去耦电容是靠近半桥顶点放,可以参考DRV8303的EVM,和DRV8301用起来是一样的,不过这个EVM设计根据典型。

3. 没有影响

4. 不影响,一个是给Buck的,一个是给门驱动的

您好!

有一个问题想咨询您一下!如果不使用8301提供的内部运放,那么DRV8301运放的相关管脚该怎么处理,是悬空还是接地?