SN65DSI85调试屏幕黑屏问题 - pll locked failed

使用SN65DSI85 MIPI TO LVDS bridge,在调试过程中,现在情况是test pattern可以显示,但是正常模式是黑屏,没有图像输出

单路MIPI 转双路LVDS

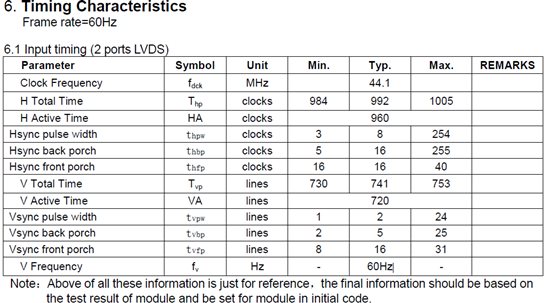

Size 10.25 inch

Resolution 1920(RGB) x 720

Interface 2-ports LVDS 24 bits VESA

从dump出来的寄存器列表看,0xe5 = 1 , sn65dsi85 pll locked failed

已经按照datasheet上的Initialization Sequence 进行init ,附件是CSR 寄存器列表

Init seq 1 After power is applied and stable, all DSI Input lanes including DSI CLK(DA x P/N, DB x P/N) MUST be driven to LP11 state.

Init seq 2 Assert the EN pin

Init seq 3 Wait for 1ms for the internal voltage regulator to stabilize

Init seq 4 Initialize all CSR registers to their appropriate values based on the implementation (The SN65DSI85 is not functional until the CSR registers are initialized)

Init seq 5 Start the DSI video stream

Init seq 6 Set the PLL_EN bit (CSR 0x0D.0)

Init seq 7 Wait for a minimum of 3 ms.

Init seq 8 Set the SOFT_RESET bit (CSR 0x09.0)

DSI CLK = 262Mhz

进行6分频 Lvds clk = 262 / 6 比较接近 LCM spec suggest clock frequency 44.1Mhz

如果Pll锁定失败,是否会导致这个黑屏的问题,应该从哪些方面去排查这个pll 锁定失败问题?

现在发现:

DSI clk 和data lane上都是有数据的;LVDS输出有clk,但是data上没有数据

该如何分析解决呢?

您好,

test pattern可以显示说明DSI85与LCD之间的连接是正常的。正常模式下黑屏有可能是输入信号或者电源质量的问题,请您检查一下DSI输入数据和时钟是否满足手册P7 6.3节中fHS_CLK,tSETUP,tHOLD这几项的要求;在检查一下电源的供电电压和噪声在工作时是否满足 VCC和VPSN这两项的要求。

Kevin

Dear Kevin Wen:

the fHS_CLK,tSETUP,tHOLD VCC和VPSN都符合datasheet上面的要求

Hi,

尝试一下以下措施:

-DSI CLK使用264MHz,Divisor为6.

-看看DSI输入是否受EMI及噪声的干扰,调整一下0x11地址的EQ值,默认为0x00无EQ,设成0x01或0x11看看有无改善。

-看看有无噪声干扰在LVDS输出和屏的输入端上,调整一下0x19地址LVDS_VOD的值。

-最重要的一点,在控制EN引脚之前(使能、禁能),确保所有的DSI信号都进入LP-11状态。否则,即使所以寄存器设置正确,且PLL Lock住了,视频信号也不会送到屏上。

Dear jacky Wang:

1、现在DSI clk 设置到265Mhz,Divison为6

2、0x11寄存器设置为0xff ;EQ设置到最大

3、0x19 LVDS_VOD值设置为0 ;200Ω near end termination

4、在assert EN之前DSI信号处于LP-11阶段

按照上面四个步骤,现在pll还是锁定失败,且LVDS data lane没有数据输出

Dear Jacky Wang:

按照如下设置之后,还是出现pll锁定失败 和 LVDS data lane无数据问题

1、DSI clk 使用265MHZ,Division为6

2、0x11设置为0xff ;clk & data lane的EQ设置为最大2db

3、0x19设置为0 ;200Ω near end termination

4、在assert en之前 DSI信号处于LP-11状态

请知悉,谢谢