请问什么情况会导致CD54HCT00F3A如下故障

时间:10-02

整理:3721RD

点击:

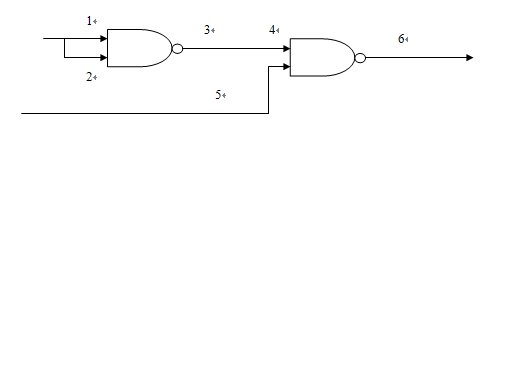

如图,我们使用CD54HCT00F3A的第一个与非门接收输入信号,第二个与非门输出作为片选信号(CS低有效),1点正常工作时输入为脉宽1.6μs,电压4.8V的脉冲信号,5脚始终接5V高电平,我们用信号发生器产生频率为312.5KHz的信号加到1脚,6脚本应输出312.5KHz低电平,用示波器观察却始终处于高电平。调节信号发生器频率到2KHz以下时,6脚输出正常,请问可能是什么情况导致故障?

另外,用示波器看过,管脚3输出正常。

首先看起来需要从频率上来分析,频率升高对单个通道逻辑功能来说不会有较大影响,整体上会造成功耗增加,即power supply。

由于datasheet中给出的数据都是内部单独测试条件下得到的,所以不好去参考。

这里请您注意看看4脚的状态,并且比较与1脚比较。 同时在频率改变中,SI 的变量中注意Tr,Tf 等参数。

当然外部走线请勿超过10cm,防止有crosstalk 较大。