DS90UB926有pclk vsync hsync,数据量却一直是0

背景:

我们设备使用DS90UB926芯片接收FPD-Link 的输入,解串后变为rgb888信号给嵌入式处理器进行采集显示;为了调试DS90UB926芯片解串功能是否正常,我们购买了DS90UB929开发板,DS90UB929开发板通过FPD-LINK线和我们的设备进行连接。

我们可以使用软件ALP软件对DS90UB929开发板进行配置

现象:

1. 如果将DS90UB929开发板配置为内部产生测试图像,即Enable Pattern Generator模式时,我们的设备是可以正确采集到信号的,图像显示正确;通过应该这个可以判断DS90UB929和我们的DS90UB926是正常工作的。

2. 如果外接HDMI信号输入给DS90UB929开发板(此时关闭了 Pattern Generator),信号给我们板上的DS90UB926解串后,发现有hsync, vsync pclk,并且这三个时钟和HDMI输入能对应上,但解串后的数据线确都是0,不知道这是什么问题导致的?

这二者serdes应该是不兼容的,929传输的FDPlink是35bit 格式:This device transmits a 35-bit symbol over a single serial pair operating up to 3.36Gbps line rate

而926接收的是28bit FPDlink mode:It receives 28-bits of data over a single serial FPD-Link II pair operating at the line rate of 420 Mbps to 1.82 Gbps.

谢谢Kailyn的回复

但我觉得929和926是兼容的,可以互相连接。

1. DS90UB926Q-Q1的手册第17页了:

The DS90UB926Q-Q1 deserializer receives 35 bits of data over a single serial FPD-Link III pair operating up to

2.975-Gbps application payload. The serial stream contains an embedded clock, video control signals, and the

DC-balanced video data and audio data which enhance signal quality to support AC coupling.

所以926也是支持35bits的。

2. DS90UB929-Q1的手册第1页也有应用框图,929和926相连

3. 当929配置为内部产生测试图像时,926是可以正确解串图像给我们的处理器

只是929外接Hdmi作为图像输入时,926解串后的数据线全为0,hsync,vsync都正确解串了,所以我觉得是不是929开发板要做什么配置。

我们试了信号发送器 笔记本作为929的hdmi输入都不可以,926解串后的数据线一直是0

抱歉,二者确实是兼容的,926同样也是支持35bit数据。

那么926输出除了数据为零,那么输出Pass, lock,PCLK引脚都正常吗?

926是否也disable了Pattern Generator(Reg 0X65)?

Pass和Lock都是高电平 , PCLK是40MHZ

926的0x64寄存器是0xe0, 0x65寄存器是0x00, 所以应该是关闭了926的pattern Generator

就数据线是0

在线等

又过了一天,问题还是没有解决,急急急

在线等

您好!针对此问题,是否有新的建议?

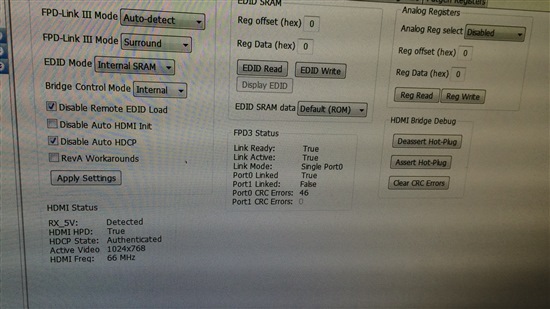

下图是926 EVM板的HDMI信息:

下图是926的0X5A的寄存器值

下图为926 EVM的配置及LED灯点亮情况,请帮忙看看配置是否正确