DS90UB925Q-Q1 PCLK波形品质确认

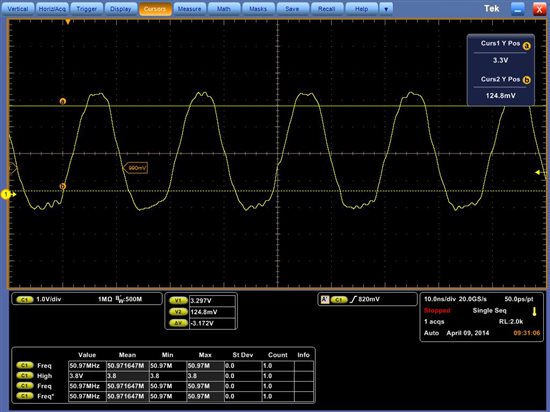

DS90UB925Q-Q1和DS90UB928Q-Q1配对使用中,925作用外部CLK,波形如下,这样的PCLK波形是OK的吗?在使用中发现用示波器探头碰下PCLK的过孔,视频会闪烁。925的DATASHEET里并没有对PCLK的波形做详细的要求,需要方波吗?

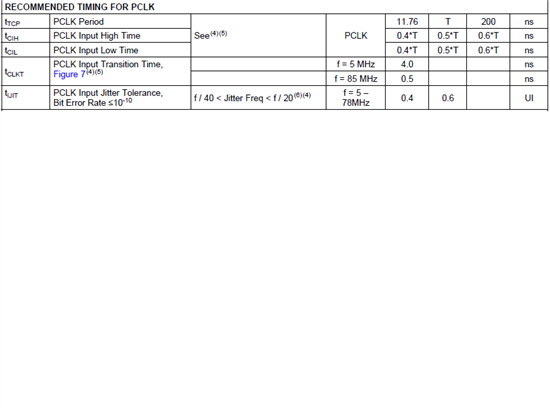

应该是个方波,你的这个波形有点失真,你可参考datasheet中Page9对PCLK的时序要求。

另外,你外部使用的什么作为PCLK?

另外,你外部使用的什么作为PCLK?

谢谢你的解答,我们外部是由TW8816的PCLK输出做为925的CLK输入。TW8816是一个视频处理IC。

在处理上,我们CLK线已经没有串接电阻或并对地电容了,但走线上有两个过孔,会不会是因为频率过大造成了失真?

换层打via也是正常的,PCLK是多大频率的?

PCLK的频率是51.2M

我们的系统为3.3V,按照式样 ,2V以上高电平,0.8V以下低电平,频率51.2M,周期为19.5ns,0.4t为7.8ns,0.6t为11.72ns

测试实际波形中,H时间为8.1ns,L时间为9.9ns,在7.8·11.72ns区间。

但是用探头,或手在PCLK上的过孔接触屏会闪。之前就算不动也会闪,925的PCLK要求很高?

我们开关日光灯屏也会闪,问题点很多。

我试过用信号发生器来产生PCLK,发现调节上升沿时也会屏闪,内部CLK和外部CLK切换的过程中也会闪,屏闪现象是一样的。因此认为和PCLK很有关系。

楼主,你好,

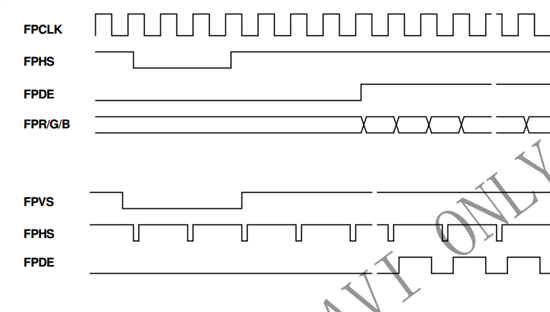

首先需要确认屏闪时,928的LOCK信号是否是异常,如果异常,说明928无法正确恢复时钟;

其次,使用内部的CLK,BIST模式下观察PASS信号和LOCK是否有异常,如果有异常,请排查链路的问题;

925对PCLK(51.2Mhz)的抖动要求(f/40到f/20之间)大概在220ps左右,可以尝试修改TW8815的分频降低pclk的抖动