LMK04800评估板的错误

snau076a.pdf的P49:Appendix C里的Power Supplies,按照图中计算的结果,LMK04800将得不到最低供电电压3.15V,LMK04800将不能正常工作。

假设6组时钟输出CLK0/1~CLK10/11全部工作于 非延迟模式、LVDS交流耦合输出。

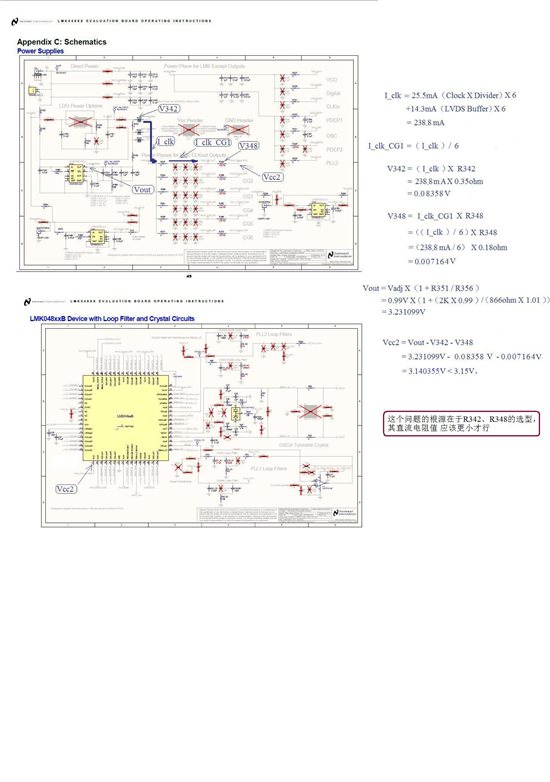

按照LMK04803的DATASHEET的Table9-9并参照9.11.1的例子,可以求出CLK0/1~10/11所需的总电流 I_clk 如下;

I_clk = 25.5mA(Clock X Divider) X 6 +14.3mA(LVDS Buffer) X 6 = 238.8mA

再参照snau076a.pdf的P59:AppendixD里的Line 40、Line 51,R342是Murata的BLM18HE102SN1D,其直流电阻值为0.35ohm;R348是Murata的BLM18AG121SN1D,其直流电阻值为0.18ohm。

那么R336上的压降为 V342 = 238.8mA X 0.35ohm = 0.08358 V;R348上的压降为V348 = (238.8mA / 6) X 0.18ohm = 0.007164 V

于是从LP3878SD-ADJ的OUT(Pin5)到 LMK04800的任一CLK供电端 例如Vcc2(P

in17)之间的压降就是 V342 + V348 = 0.08358 V + 0.007164 V = 0.090744 V

参照snau076a.pdf的P60:AppendixD里的Line 53、Line 54,R351、R356是1%精度电阻;再参照LP3878SD-ADJ的DATASHEET,Vadj(min) = 0.99V

那么在最坏情况下,LP3878SD-ADJ的 Vout = Vadj X(1 + R351 / R356 )= 0.99V X (1 + (2K X 0.99 )/ (866ohm X 1.01 ))= 3.231099V

于是LMK04800的Vcc2(Pin17)= Vout - V342 - V348 = 3.231099V - 0.090744V = 3.140355V < 3.15V。

由上可知,LMK04800将得不到最低工作电压,将不能正常工作。

上述计算尚未考虑 延迟模块的使用、LVPECL模式的使用,若是将 延迟模块的功耗、LVPECL模式的功耗 考虑进去的话,Vcc2只能更低,甚至可能在正常情况下,LMK04800都无法工作。

这个问题的根源在于R342、R348的选型,其直流电阻值应该更小才行。

附图如下

我现在遇到的问题就是:如何选择R342、R348的型号,才能满足LMK04800的正常工作所需的供电电压呢?

我的设计情况是:6组时钟(Clk0/1~Clk10/11)全部启用,输出模式都是LVPECL,延迟也全部启用。

评估板中,LMK04800的供电有2个电源芯片可选:LM317AEMP与LP3878SD-ADJ。

从snau076a.pdf的P58的Line 13、P60的Line 50可知,R338的精度是5%、R344的精度是1%。

LM317AEMP在最坏情况下的输出 Vout = Vref ( 1+ R344 / R338 )= 1.225V (1 +(392 X 0.99)/(240 X 1.05))= 3.1115V。

即便R338也是1%精度,Vout也就是3.1862128V。

可见LM317AEMP要比LP3878SD-ADJ还差(LP3878SD-ADJ最坏情况下的输出为3.231099V)。

不知是否 因为这个原因,才选择了LP3878SD-ADJ而不是LM317AEMP给LMK04800供电。

Hi James,

你考虑的很细,为了避免你这种情况,按照你的计算,你可以在LDO上选用稍小一些的R2,这样最差情况下电压也能满足你的需求。

改动R1/R2之后,Vout的输出得到了提升,确实可以满足CLK部分的供电电压(VccCLKoutPlane),但是同时又超过了PLL部分的供电电压(VccPLLPlane),因为PLL部分所需供电电流比CLK部分要小,提升Vout导致PLL部分的供电电压(VccPLLPlane)过高。

咋办呢?