求助:cdce62005失锁

大家好:

最近新焊接了一批6678的板卡,发现JTAG无法连接,后来发现是时钟没有锁住,前几次上电还可以锁住,之后再上电就无法锁住,lock信号波形是600KHz左右的脉冲。

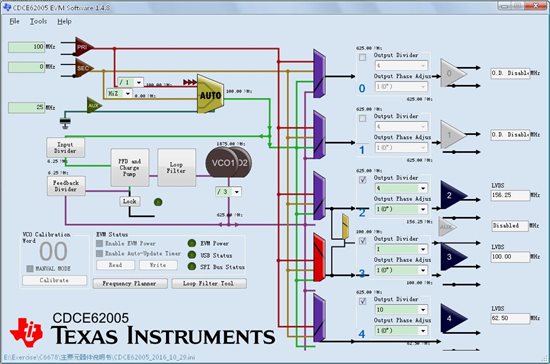

时钟部分参考的EVM板,使用的是cdce62005,100MHz输入,输出156.25MHz、100MHz和62.5MHz。SPI读写时序是用FPGA做的,一样的时序,一样的配置文件,在老批次板卡里是好的。

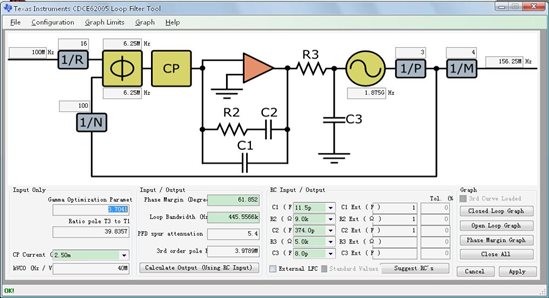

后来检查配置文件,发现配置文件里的Loop Filter里有告警。之前也没有理过Loop Filter,只是在Frequency Planner中计算出了输出频率,之后就直接将各寄存器的值写进去了。为了消除告警,使用了GUI的推荐值,之后告警消失。但是还是无法锁住。后来使用了手动校准,也就是在unlock命令后操作reg6的bit22。基本每次都能锁住。但是在运行一段时间后,lock有时会出现低脉冲,宽度在0.2us~1us之间不等。

不知道问题出在哪里?感觉像是是配置文件的问题,不过不知道还需要怎么修改?请帮忙分析一下,谢谢各位!

主界面配置如下

Loop Filter如下

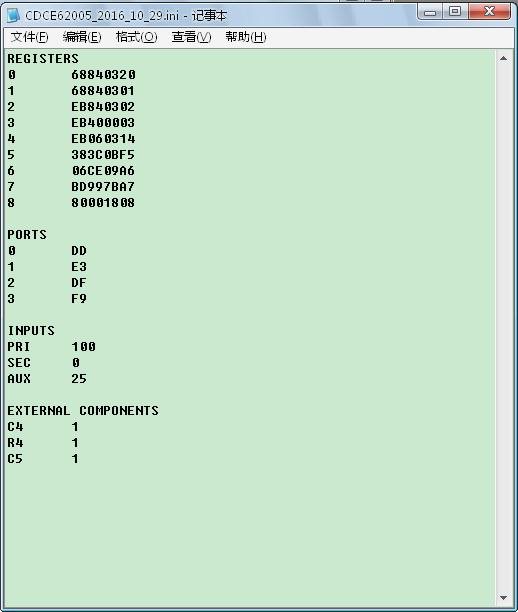

寄存器如下

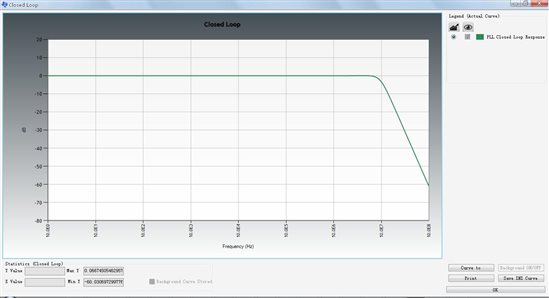

闭环增益如下

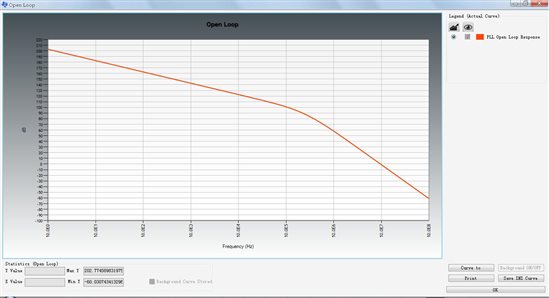

开环增益如下

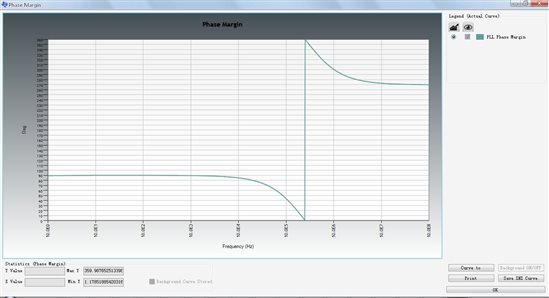

相位裕量如下

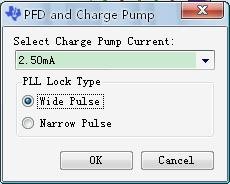

PFD设置如下。不知道这个lock type是什么意思,脉宽大小会有什么影响?

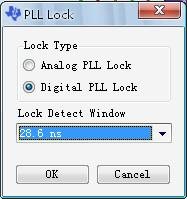

PLL Lock设置如下,选的最大窗口。不知道analog和digital有什么区别

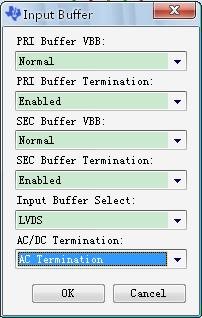

input如下。

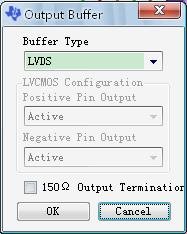

output如下,不知道这个150ohm的端接是什么意思。在要写的配置文件里,也没有看到相关说明

TI的技术支持在吗?还有其他大牛吗?

你好,

如果你确定寄存器和loop filter都是按我们的软件推荐值来设计的,包括电荷泵电流,鉴相频率等各种参数,请检查输入参考时钟的频率和幅度是否满足要求。

您好,你的100MHz输入是来源一个晶振还是另一片62005?

一个差分晶振