CDCM6208失锁

各位高手,我最近设计的板卡上用到了CDCM6208V1给DSP供时钟,目前遇到了PLL不能锁定的情况。

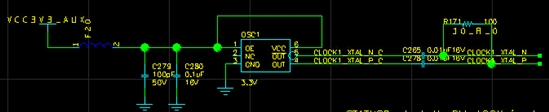

时钟源是30.72MHz的差分晶振,LVDS电平,原理图部分如下:

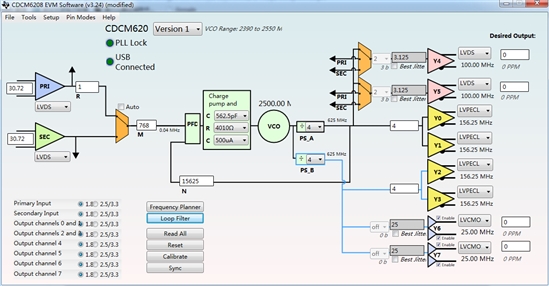

为了配置简单,我采用了Pin_mode模式,参考datasheet查表选择合适的输出时钟频率,通过对PIN0~4进行上拉下拉完成配置。我采用的PinMode 31-V1如下图:

上电之后,PLL_LOCK大概5s之后才能上来,过了10s之后就掉下去了,实测各输出时钟均低于设定值,比如25MHz测得为23.8MHz,156.25MHz测得为140MHz左右。

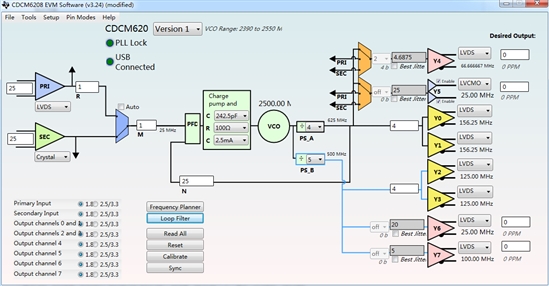

我把30.72MHz的差分晶振换做25MHz的差分晶振,采用PinMode 19-V1如下:

上电后PLL立刻锁住,各输出时钟实测均正确。请问这是怎么回事呢?

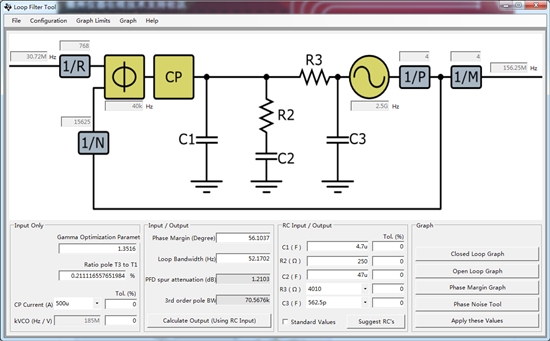

30.72MHz的环路滤波参数如下:

输入为25MHz的时候环路滤波参数如下:

自己再顶一下。我可以通过飞线把PIN_MODE改成SPI_mode,SPI的几条线接到一片CPLD上面。但是我通过CPLD配置CDCM6208总是失败,测得各个时钟输出端口的频率都是SPI模式的默认频率,应该就是没有写进去。程序采用VHDL编写,求大神帮忙看一下,能帮忙修改或者有现成的VHDL或者Verilog程序就更好了!不胜感激!

0336.CDCM6208_SPI.rar

30.72MH和25MH的参考时钟信号幅度有区别吗?

你好,两者采用的差分晶振封装相同,30.72MHz的信号幅度为0.9V左右,峰峰值170mV;25MHz的幅度1.2V左右,峰峰值60mV。这个会影响PLL的锁定么?

30.72MHz的信号幅度为0.9V左右,峰峰值170mV;25MHz的幅度1.2V左右,峰峰值60mV --------- 幅度与峰峰值是啥关系呢?LZ可否画个示意图?

我揣测是共模电压是0.9V,PP值是170mV

不好意思,应该是我表达有误。应该是30.72MHz的共模电压为0.9V左右,峰峰值170mV;25MHz的共模电压1.2V左右,峰峰值60mV。o(╯□╰)o……

liu:

咨询一个基础问题哈!晶振输出时钟信号共模电压达不到1.2V,是不是会很大程度上影响时钟芯片的锁定?

晶振输出采取隔直措施,去除直流电平问题

4744.6208spi_cfg.txt

4274.CDCM6208_Settings_2015_1_28.ini

有高手能够帮我看一下这个CDCM6208的SPI配置程序么?我用的是一片CPLD,但是写寄存器总是不成功。寄存器值通过CDCM6208 EVM Software配置产生。

你好,这个芯片用PIN MODE还需要软件进行配置吗?你那个软件界面是配置什么的,配置好以后通过SPI或者I2C写入?

您好,有个问题请教一下,这个CDCM6208的PIN MODE模式还是需要软件进行配置一下?是配置什么,配置好以后通过SPI或I2C写入吗?不配置不可以吗?

你好,PIN MODE不需要软件额外配置的,界面只是表明现在的配置状态。通过SPI或者I2C写入需要SI_MODE为00。

请问一下,你的时钟通过spi可以配置成功不,可以的话请教一下啊

你好,我通过一片CPLD配置CDCM6208目前没有成功,通过MCU的研华好像就提供了程序吧,不知道你的设计是什么样的呢。通过了求分享哈!

感谢回复!