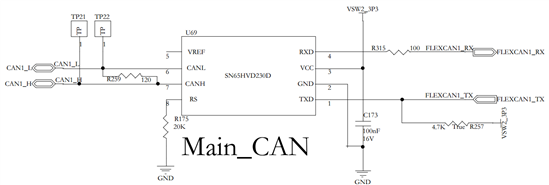

3.3V CAN收发器:SN65HVD230 输出的隐性电平无法到达2.3V,为什么会出现这种状况呢?,求解决方法

时间:10-02

整理:3721RD

点击:

原理图:

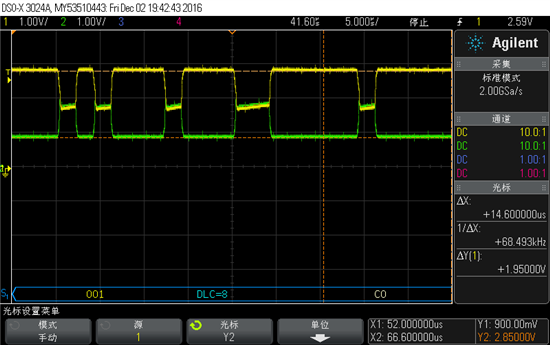

测试结果:

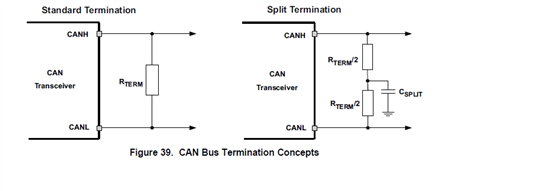

电路中采用的标准的端接方法,建议采用第二种端接方法试下,split termination,两个电阻为60ohm,Csplit=4.7nF。

分离式端接这种方法已经验证,共模噪声有改善,但是隐性电平还是无法无法到达2.3V,只有2V。还有什么方法能让隐性电平调节到2.3V吗,是芯片的设计问题吗?

差0.3V,这或许跟您电路设计中存在一些干扰有关,如PCB走线或电源毛刺,这颗芯片已经量产,理论上不会出现什么问题。