FPD LINK III 940 949的问题

关于949 和940 配对使用的问题,手册上说的GPIO[8:5]是寄存器类型GPIO,与GPIO[3:0]的区别在哪里?

“

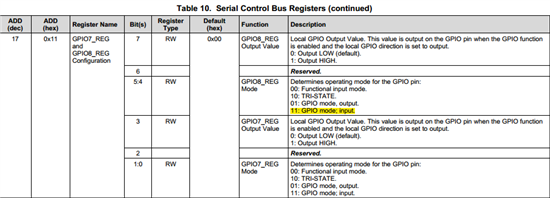

8.3.15.3 GPIO_REG[8:5] Configuration

GPIO_REG[8:5] are register-only GPIOs and may be programmed as outputs or read as inputs through local

register bits only. Where applicable, these bits are shared with I2S pins and will override I2S input if enabled into

GPIO_REG mode. See Table 3 for GPIO enable and configuration.

Note: Local GPIO value may be configured and read either through local register access, or remote register

access through the Bidirectional Control Channel. Configuration and state of these pins are not transported from

serializer to deserializer as is the case for GPIO[3:0].

”

根据手册上这段话的意思,GPIO_REG[8:5]只能通过本地寄存器进行读取,而GPIO[3:0]寄存器的读取既可以从本地寄存器,也可以从remote 寄存器读取(比如serdes搭配使用的时候,一个是local, 另一个是remote),但是注意GPIO[3:0]的引脚配置只是针对本地的而非remote,比如940的GPIO[3:0]的配置不能用在949的GPIO[3:0]上面,因此说Configuration and state of these pins are not transported from serializer to deserializer as is the case for GPIO[3:0].

按照你的解释我有以下的推断不知道对不对

“Note: Local GPIO value may be configured and read either through local register access, or remote register

access through the Bidirectional Control Channel. ”

940 的GPIO[3:0]和940 的GPIO[8:5]都能通过 ser端比如949通过940的 Bidirectional Control Channel 配置,Bidirectional Control Channel是通过 FPD LINK III进行传输。

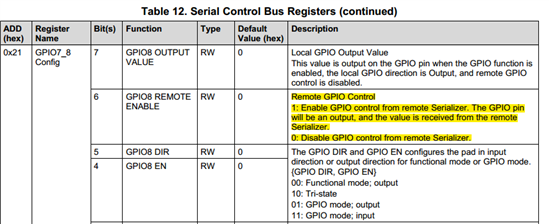

比如对于GPIO8

949端设置

940端设置通过948设置

是不是此时949设置gpio8为高,此时940的gpio8就为高了?

抑或是通过949设置940的0x21第7位为高?

将940的0x21寄存器的bit6=1设置为高之后,是940的GPIO设置是来自949(serializer)的GPIO设置.

另外,你可以看下949的GPIO[8:5]寄存器0x10,0x11,就没有Enable Remote GPIO控制,只是作为输入输出模式,就是您的第一个问题中提到的local GPIO[8:5]和GPIO[3:0]的区别。

多谢kailyn chen的回复.

总结您给出的信息,那么是否就可以这么理解:

949 端的GPIO input 信息GPIO[8:5]或者GPIO[3:0]都可以通过 FPD link III 发送到940 端。但是反向的话,只有GPIO[3:0]可以从940 传递到949作为949的output?另:kailyn 是否可以与你通过邮件交流下,我的邮箱是taojiang6 at iflytek.com