CDCE937读取寄存器数据不对!

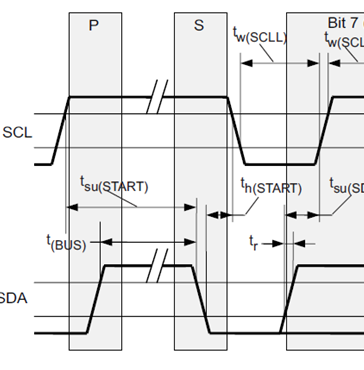

时钟源芯片CDCE937,内部有EEPROM,接口采用类I2C协议,主要在时序上与专用EEPROM略有差别,尤其是在开始和结束的建立时间上,要求4.7us,而整个SCL高电平为5us(100kHz频率对应10us周期)。

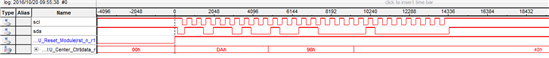

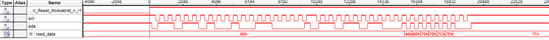

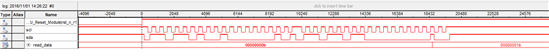

现在用FPGA控制芯片,写好了写入时序部分,利用TI-pro配置软件,生成HEX文件来初始化rom,写入CDCE937,写入成功,通过signalTap观察没问题,并且能正确输出想要的频率。写入成功后,想验证读取功能,发现读取的寄存器数据有异常(与写入的不对)。所以就做了如下实验,在offset为18H的寄存器中,单字节写入40H,然后读取18H的寄存器,结果显示是7FH。这两个过程没有断电,只是重新烧写了FPGA程序,因为现在写和读是两个工程。

这是问题一:写入肯定没问题,因为芯片都能按照预想工作,那读取又是在哪里出问题了呢?

问题二:每次断电,写入的数据都还原了。怎样锁存EEPROM写入的程序,使得第二次上电,它依然按照配置的频率输出。是配置EELOCK这个位吗?

问题三:如果寄存器被锁住,不再使用scl/sda,那么S0 S1 S2是不是就是按照datasheet中的7种状态配置,实现某种状态输出?

谢谢!

如果配置了EELOCK这个位为高的话,EEPROM将被永久锁存,但是仍然可以往寄存器里配置新的数据,只是这数据将不再保存。

所以确认下是否已经对这位进行配置,导致每次断电之后写入的数据都还原。

不用SCL/SDA的话,可以通过S0,S1,S2三个控制引脚进行下面这些配置:

• Spread spectrum clocking selection → spread type and spread amount selection

• Frequency selection → switching between any of two user-defined frequencies

• Output state selection → output configuration and power down control

然后结合Table8中S0~S2的八种设置对应的不同配置,可以看出是可以实现7种状态输出的某一种的。

嗯,这个问题。我有留意过……我在写入配置数据以后,并没有断电。并且读取过EELOCK位所在的字节,它确实为0(字节为0000_0001)。请问如果EELOCK位确认为0,那么每次写完数据,是不是断电重启后,会保留上一次的写入数据?

另外,如果用FPGA控制的话,由于需要配置的寄存器较多,我用TI-PRO生成了一组配置之后,保存为HEX文件,然后倒入FPGA的ROM,最后FPGA从ROM中读取并写入CDCE937,这种方法是可行的吧?