CDCE62005的可以锁住却没有输出

时间:10-02

整理:3721RD

点击:

现在情况是一:不管什么频率的LVCMOS输出都没问题。二:低于125M的LVDS输出也没问题。三:高于125M的LVDS输出没有,一直为高电平,pll lock有效状态为高所以应该锁住了,AUX_OUT正常输出说明VCO的输出应该没问题,所要通道的高于125M的LVDS输出却没有,现在不理解为什么到了后面的分频却不行了。而且把输出改成LVCMOS,其他都没改却可以正常输出,个人感觉out block的寄存器设置没有问题,LVCMOS的都能正常输出,只是改成LVDS却不行。实在是找不到原因了,求专家支招!

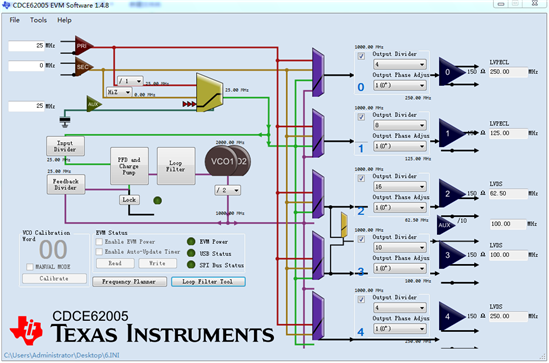

高于125M LVDS时,输入多少频率?是不是没在VCO频率范围之内? 用CDCE62005 GUI进行配置的吗?

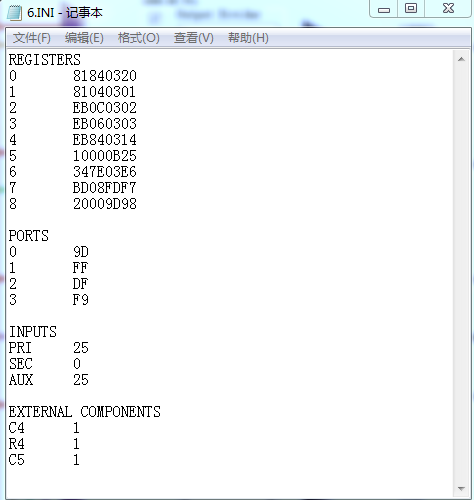

非常感谢您的回复与解答。现在输入是25M的晶振输入,VCO频率为2000M 选的是VCO1,是用的GUI配置的,loop filter没有任何警告信息。现在就是用SPI接口直接写进ram中然后测量输出的,并没有进行校准与同步设置,不知道会不会有影响。既然LVCMOS的都能正常输出,为什么LVDS的就不行呢。为什么125M的LVDS考研正常输出,而250M这样的输出却不可以,仅仅是改了最后输出模块的分频

能把GUI的配置的拷屏发上来吗?大家一起看一下

前两个是GUI配置图。最后是寄存器的值。非常感谢!