DS90UB925和DS90UB926无法Lock。

我遇到一个问题,DS90UB926无法解析DS90UB925的信号,两者无法LOCK上。请大神们帮我看看分析一下问题在哪吧。

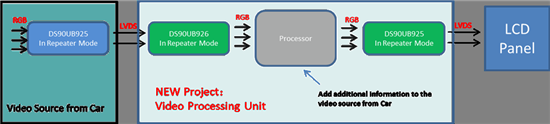

正题的框图如下。我的板子上有一片DS90UB926,他从外面的板子(板子A)上的DS90UB925获得信号给到FPGA,FPGA做处理后给到板子上的925,再给到另外一块板子(板子B)上的926.

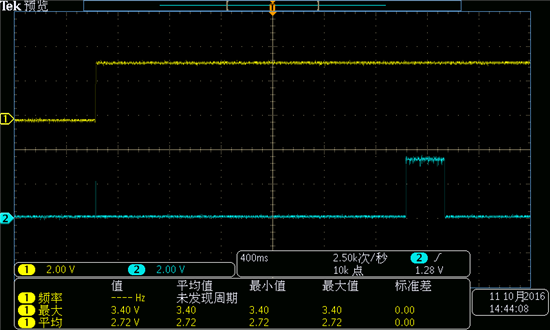

但是现在A板子的926和我们的板子上的926连接不成功。硬件上肯定是通的,可以测到信号。现在只在上电后几秒时LOCK输出一个300ms左右的高电平,之后就一直是低电平,RGB引脚也没有输出。下图是上电时VDD(1通道)和LOCK引脚(通道2)的波形

我们做过以下的测试和尝试:

1、926的I2C通信是OK的,可以读到里面的ID和配置模式等,写入一些寄存器也能成功读出来。

2、只有把Mode_SEL配置为模式9的时候LOCK是高的,也就是LOCK成功,但是这个时候926的输出是错误的,VS,HS和DE输出都是16M

3、更换过926的芯片,现象一样。

4、直接把B板子与A板子相连,B板子上的926与A板子上的925能成功相连并正常工作。所以A板子的925的输出是正常的

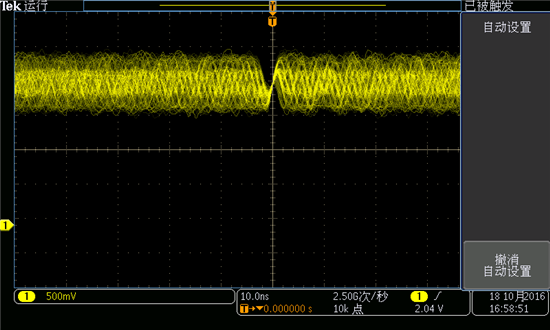

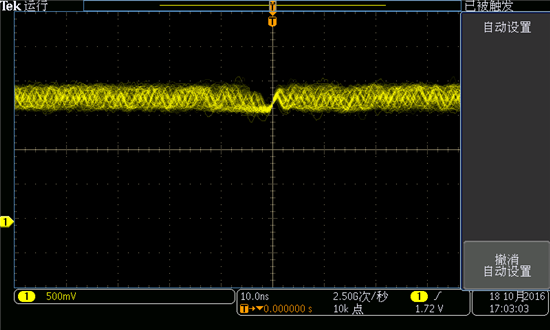

5、我们测了我们的板子和B板子上926RIN+/-引脚对地的波形(正常应该测两个的差分眼图,但是目前没有条件),发现二者的波形形状差不多,但是B板子上的波形峰峰值是我们板子的大约1半,这个有影响吗?

我们的板子

B板子

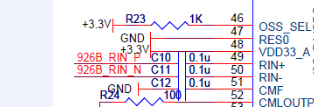

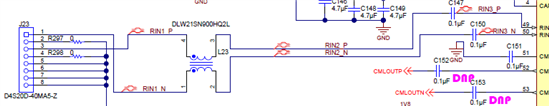

6、对比我们的板子与参考设计的原理,发现在RIN+/-上有一些区别:我们的设计里只加了隔直电容,参考设计里还加了共模电感,B板子(不是参考设计)还各自串了一个电阻。请问这个需要严格按照参考设计来吗

我的板子

参考设计

Luffy,

你的描述不是很清晰,很难理解你的系统架构,能在框图中表明A板,B板,你自己的,他的,还有外面的板子是哪一部分吗?

1. 这说明926本身的焊接和外围电路没问题。

2. 前端925的输入PCLK频率是多少?是否看过PCLK的波形质量?

4. 你是指间PCB之间原来的使用较长的线缆连接,现在去掉线缆了吗?

通常LCOK引脚不锁定,我们要检查

1. SER 925输入端的Clock,data,sync 信号是否稳定并满足925的spec要求

2. 线缆,连接器的连接是否正确

3. DES 926 输入端的差分信号眼图是否满足spec要求。

Kevin